## Description

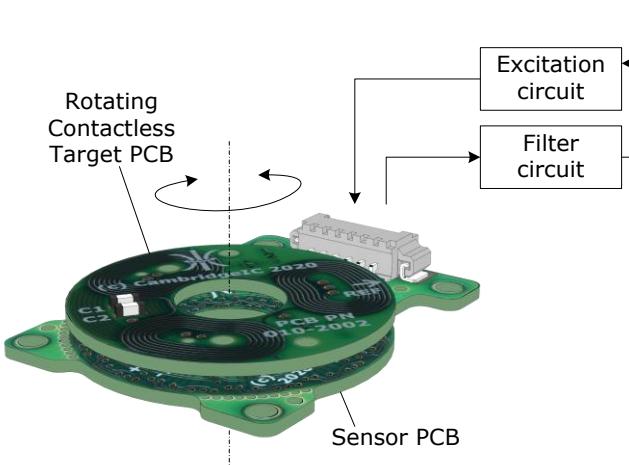

CambridgeIC's CAM622 is a Resonant Inductive Encoder IC. It includes a Sensing Engine for measuring contactless position, and an Interface Processor that can generate encoder style outputs.

The Sensing Engine connects to an external sensor. This detects the position of a contactless inductive resonant target. Both sensor and target are made from PCBs. They include coil patterns for resonant inductive sensing. These are available from CambridgeIC, so customers can manufacture the parts themselves and integrate them with their product. The CAM622 works with a variety of different sensor and target sizes.

The Interface Processor can generate encoder style digital outputs, using an SPI interface for configuration and diagnostics. A host may alternatively use SPI as the primary interface, reading measurement results at high speed.

## Features

- Works with CambridgeIC's "Type B" sensor PCBs

- Fully ratiometric Sensing Engine

- Automatic tuning to target frequency

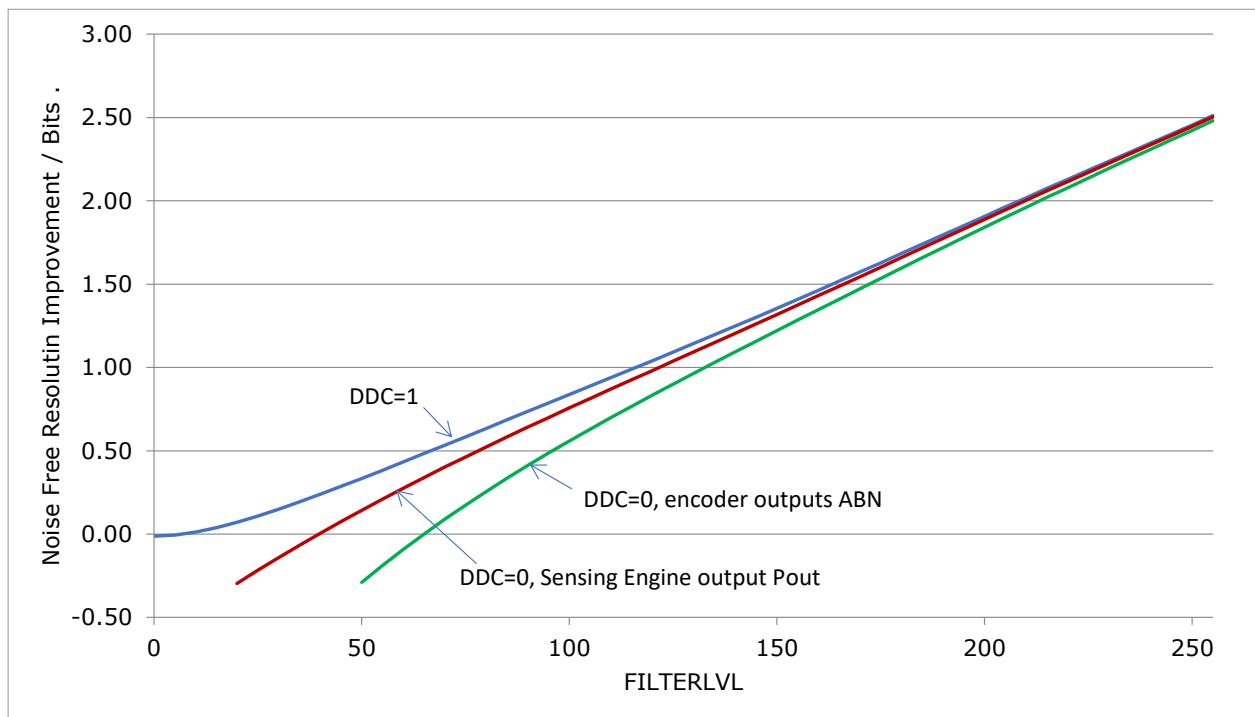

- Optional adaptive filter for extra resolution

- Filter can be configured for zero phase delay

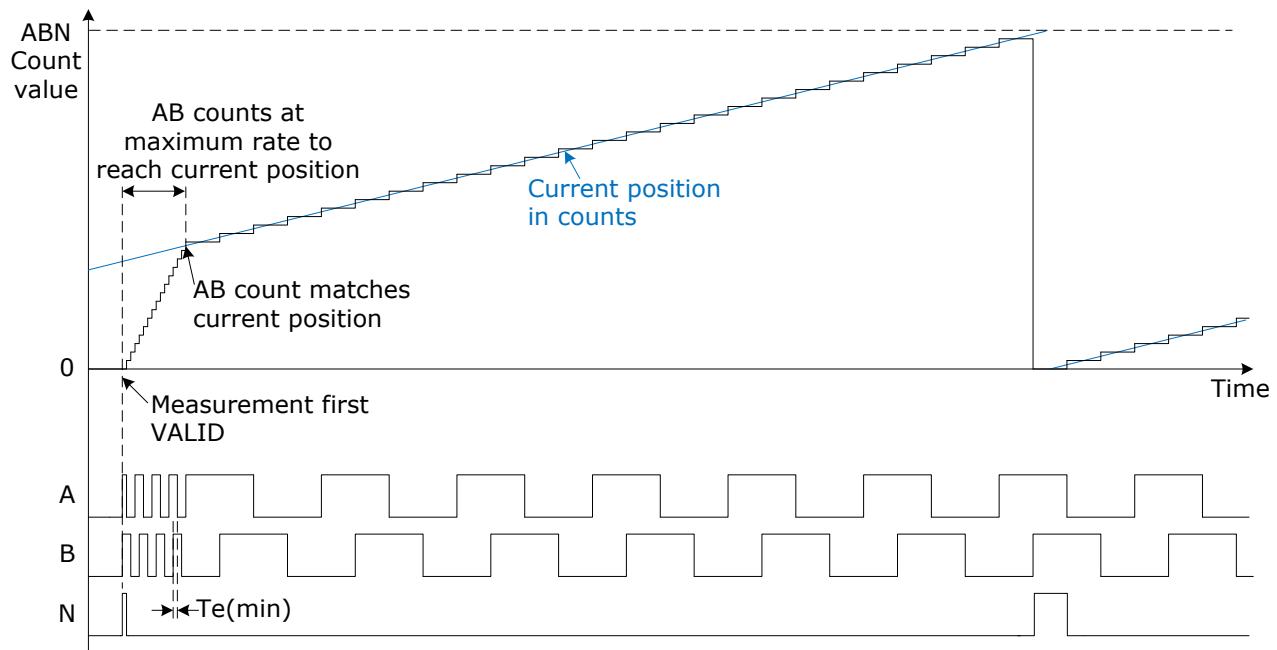

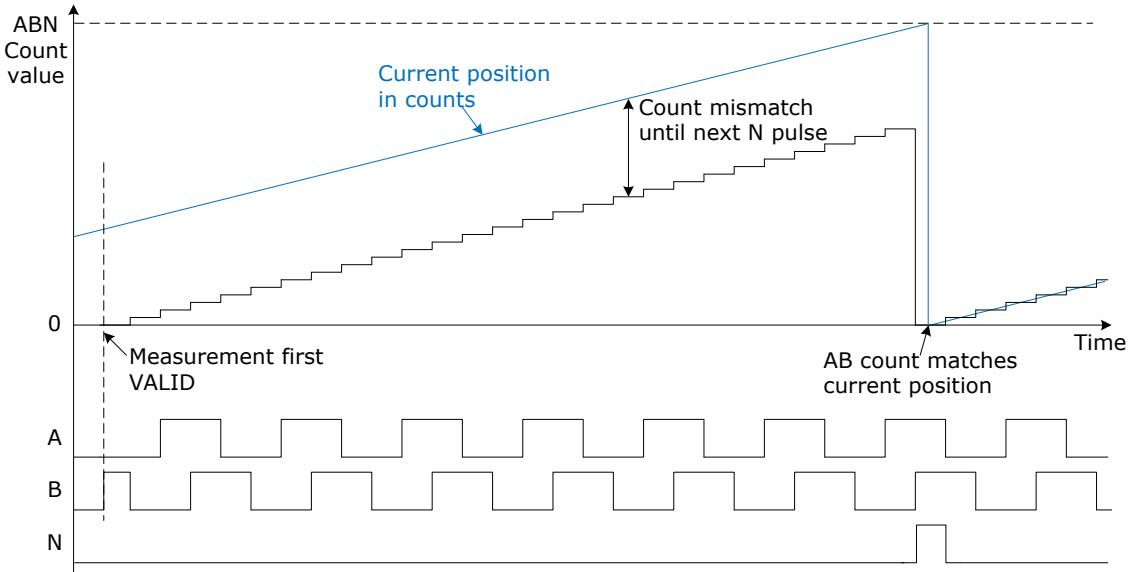

- Encoder style ABN outputs with True Edge Timing

- ABN outputs absolute at start-up (NSTART=1)

- SPI for configuration or reading results

- BiSS interface support

- Internal software upgradable over SPI

- Exceptionally stable across temperature

## Performance

- Up to 33000 position samples per second

- Resonator frequency tuning range  $\pm 8\%$

- ABN cycles/rev configurable up to 16384

- Tested to 66,000rpm (at 1000 AB cycles/rev)

- AB Edge Rate up to 4.5MHz (4170rpm at 16 bits)

Figure 3 CAM622 function overview

| Product identification |                            |

|------------------------|----------------------------|

| Part no.               | Description                |

| CAM622UE               | 28-pin UQFN -40°C to 125°C |

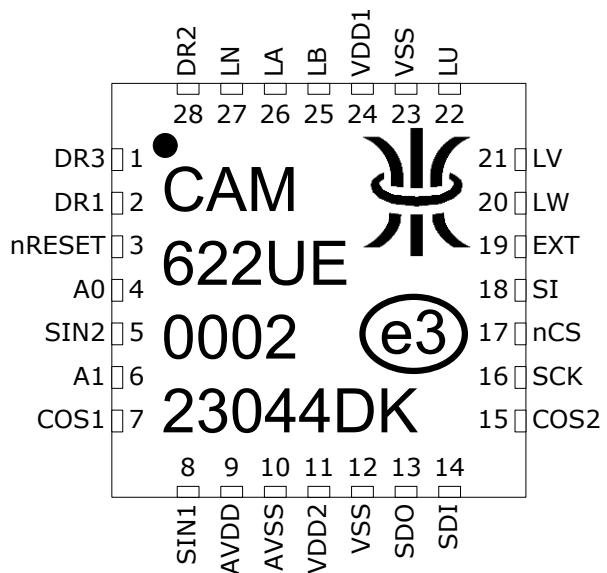

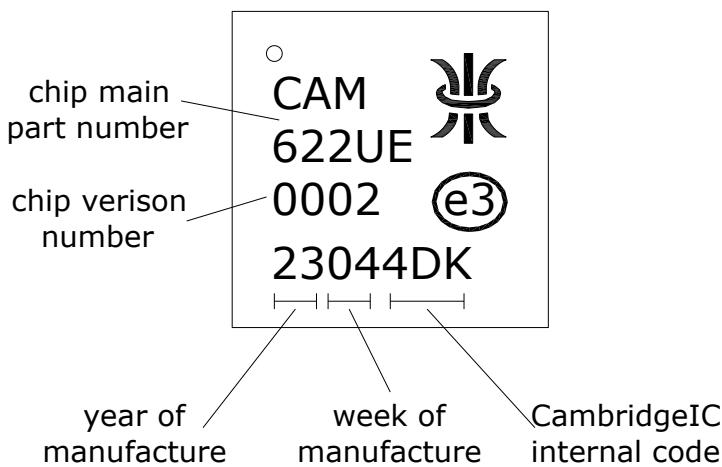

Figure 1 CAM622UE image

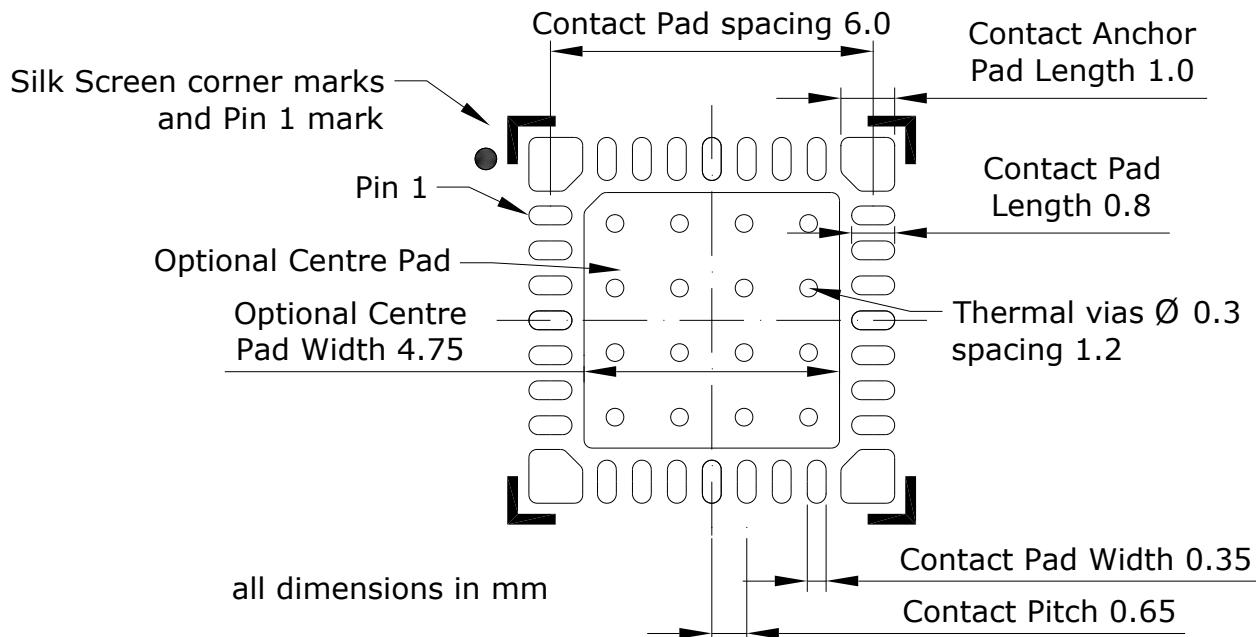

Figure 2 CAM622UE 28-pin SSOP pinout

## 1 Functional Description

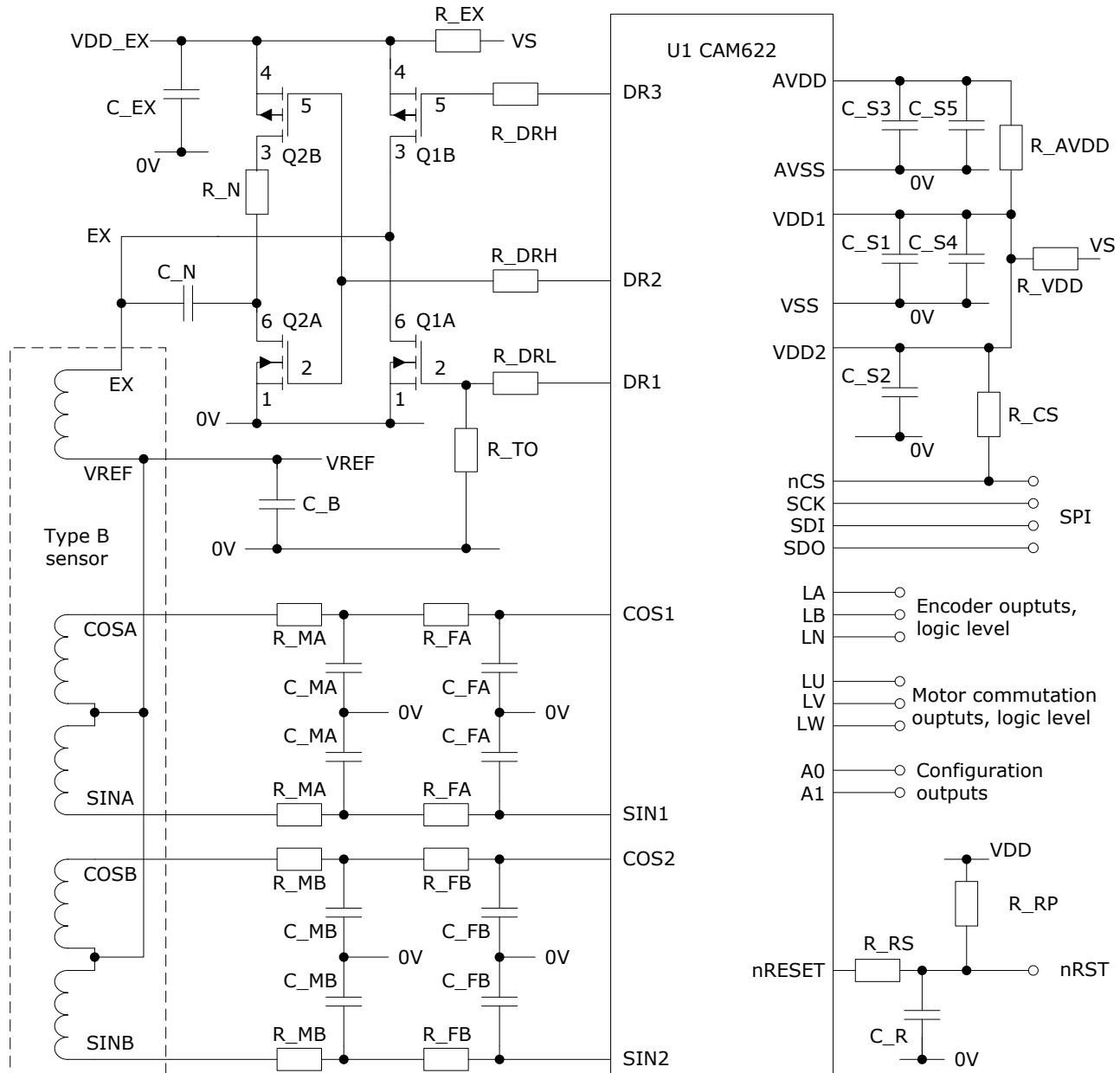

Figure 3 shows an overall block diagram of the CAM622, sensor and external circuitry.

Please refer to section 3 for details of the external circuitry required, including the excitation circuit and filter circuit.

### 1.1 Type B Sensor Overview

The CAM622 works with Type B Sensors. Please refer to a Type B sensor's datasheet for more details of its operation and performance. Please refer to the Type B Sensor Reference Manual for the principle of operation of Type B sensors, and for sensor integration guidelines.

Sensors and targets are both built from conventional PCBs. The sensor comprises 3 or 5 printed coils, and is connected to CAM622 circuitry. The target is an electrical resonator and comprises one printed coil connected to one or more resonator capacitors. The target has no electrical or mechanical connection to the sensor.

Sensors include an excitation (EX) coil that is used to energise the resonator inside the target.

Type B sensors each have a Subtype. When this is non-zero, this indicates that the sensor includes fine (COSA, SINA) and coarse (COSB, SINB) sensor coils. The Subtype is the number of sinusoidal repeats of the fine coil across 360° mechanical rotation. The coarse coils have one sinusoidal repeat across 360° mechanical rotation.

### 1.2 Sensing Engine Description

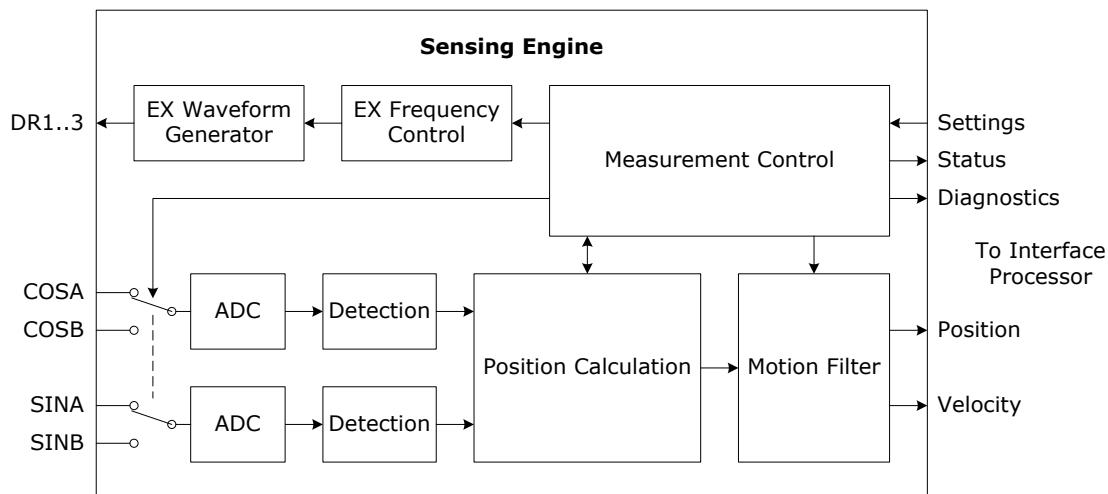

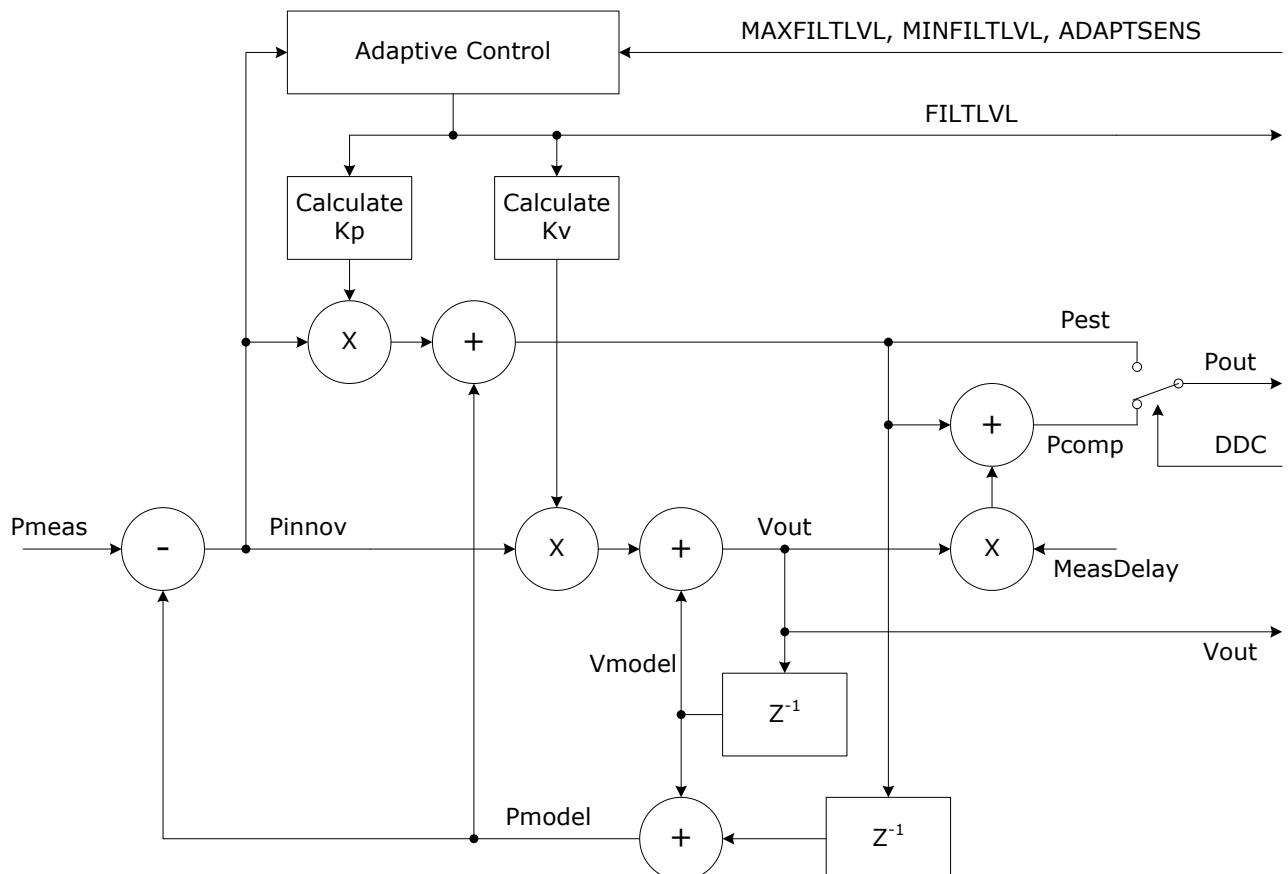

**Figure 4 Sensing Engine block diagram**

The purpose of the Sensing Engine is to energise the sensor and process its return signals to yield position and velocity data.

The Sensing Engine includes an EX Waveform Generator that outputs the DR1...3 signals used to drive the excitation circuit. It is fully digital and its precise frequency and timing are under the control of an EX Frequency Control block. The target's resonator has a high Q-factor, which means that the frequency of the energising current must closely match its resonant frequency for efficient power transfer. The EX Frequency Control block includes a control loop to maintain a match between the EX Waveform Generator's output frequency and the resonator's frequency.

Signals from the sensor coils are converted to digital signals with ADCs. This allows all remaining processing to be done in the digital domain, for precision and reliability. A multiplexer scheme allows the ADCs to either measure fine sensor coil signals (COSA, SINA) or coarse sensor coil signals (COSB, SINB). A Measurement Control block selects which coils are connected for any given measurement.

Detection blocks process ADC results, and yield data on signal amplitude, frequency and phase. These blocks have a wide but finite frequency range, and this determines the extent to which the Sensing Engine can tolerate resonator frequency variation. This is specified in section 4.

Frequency data from these detection blocks is passed to the EX Frequency Control block, to close the EX frequency control loop and keep the EX frequency matching the resonator frequency.

Signal amplitude and phase data is passed to the Position Calculation block. This manipulates the data in a precise, ratiometric way to yield measurements of the target's position.

Most position measurements are taken using data from the fine coils. Measurements from the coarse coils are only taken at start-up, to first establish absolute position, and again at regular intervals as a cross check. That interval is under the control of the ABSSEL control, see section 6.4. The Position Calculation block combines fine and coarse measurement data to ensure that its output remains absolute across 360° all of the time.

The Sensing Engine's measurement process is extremely rapid, typically repeating with an interval as little as 30µs (see section 6.5).

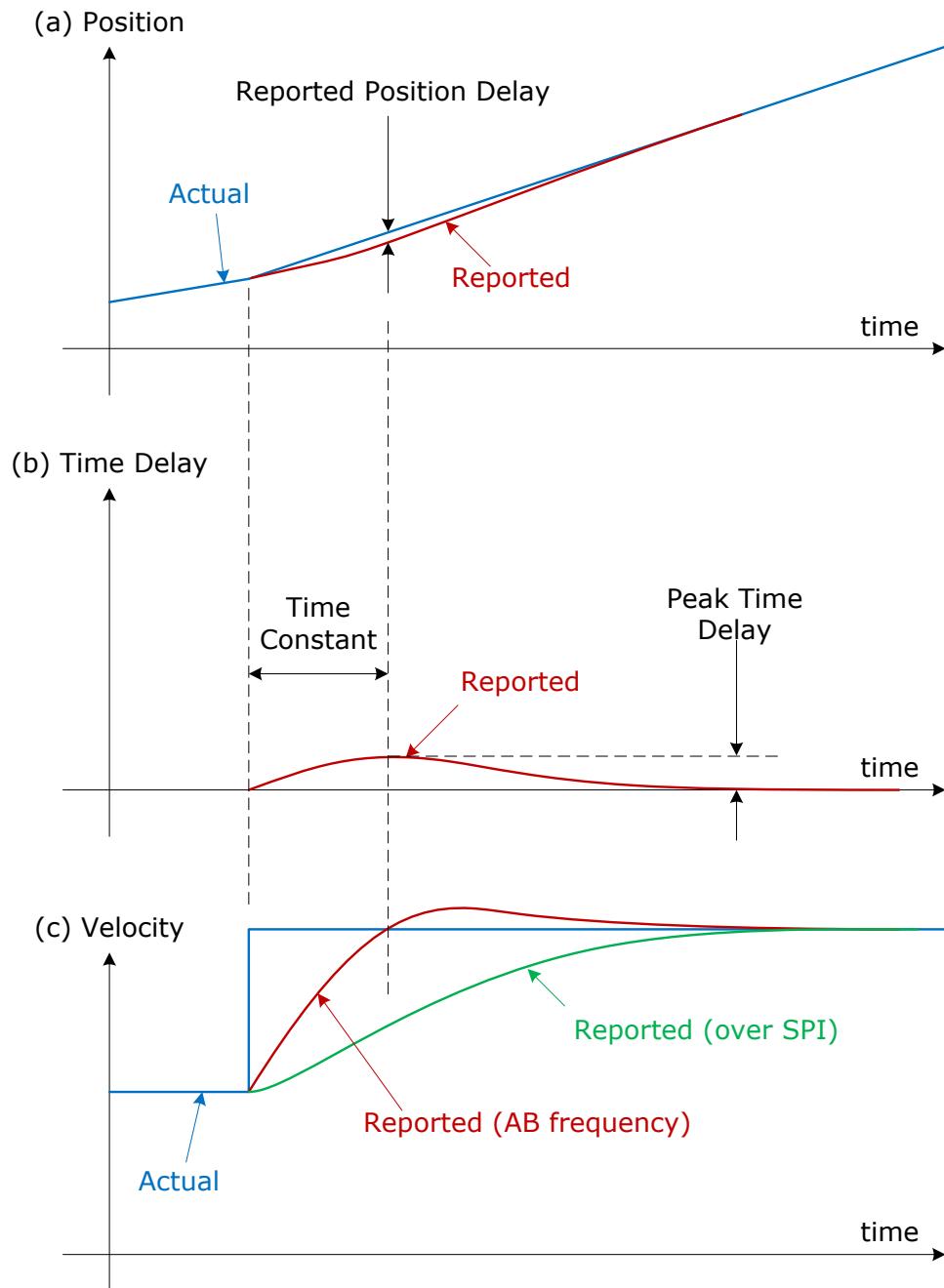

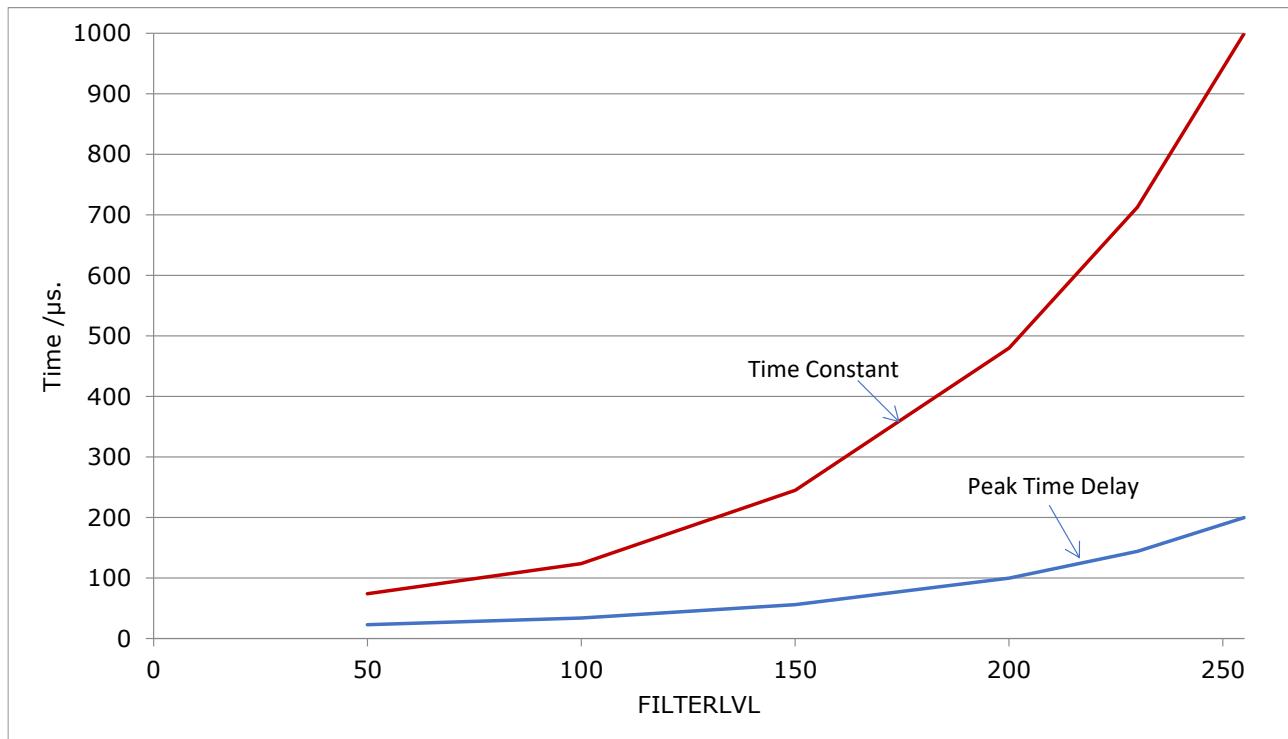

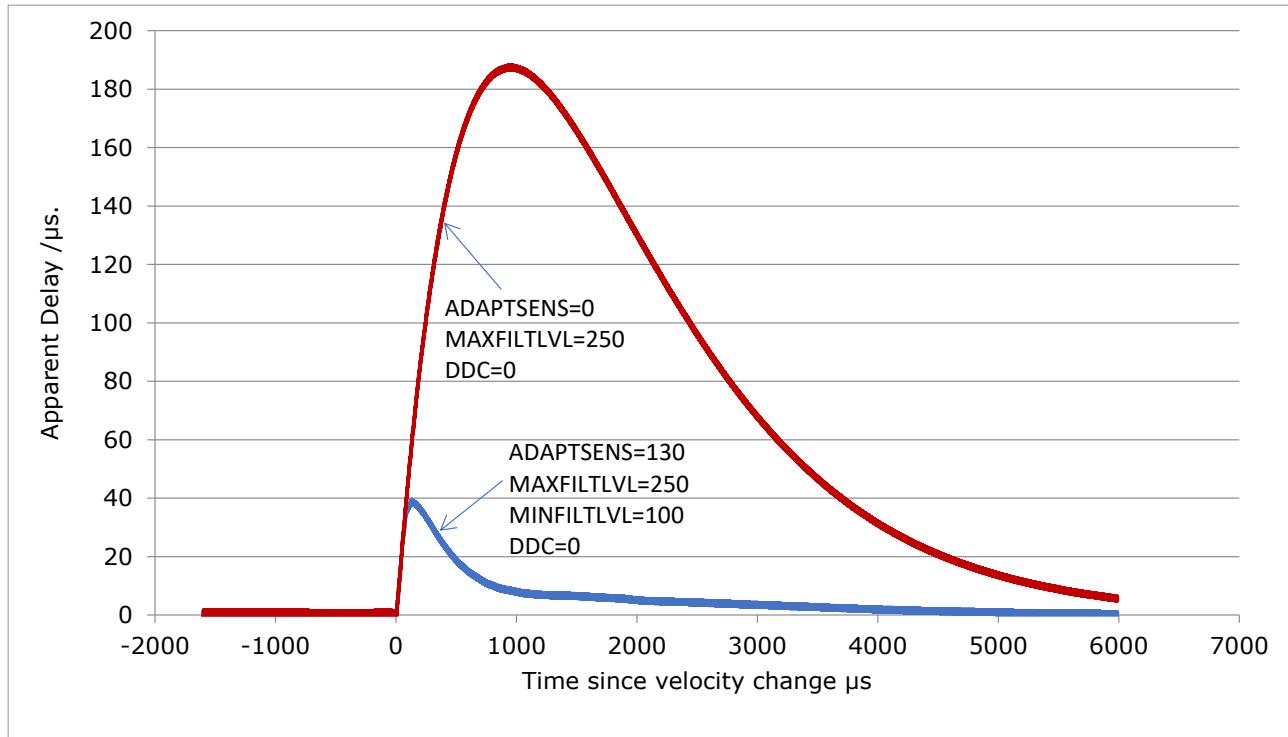

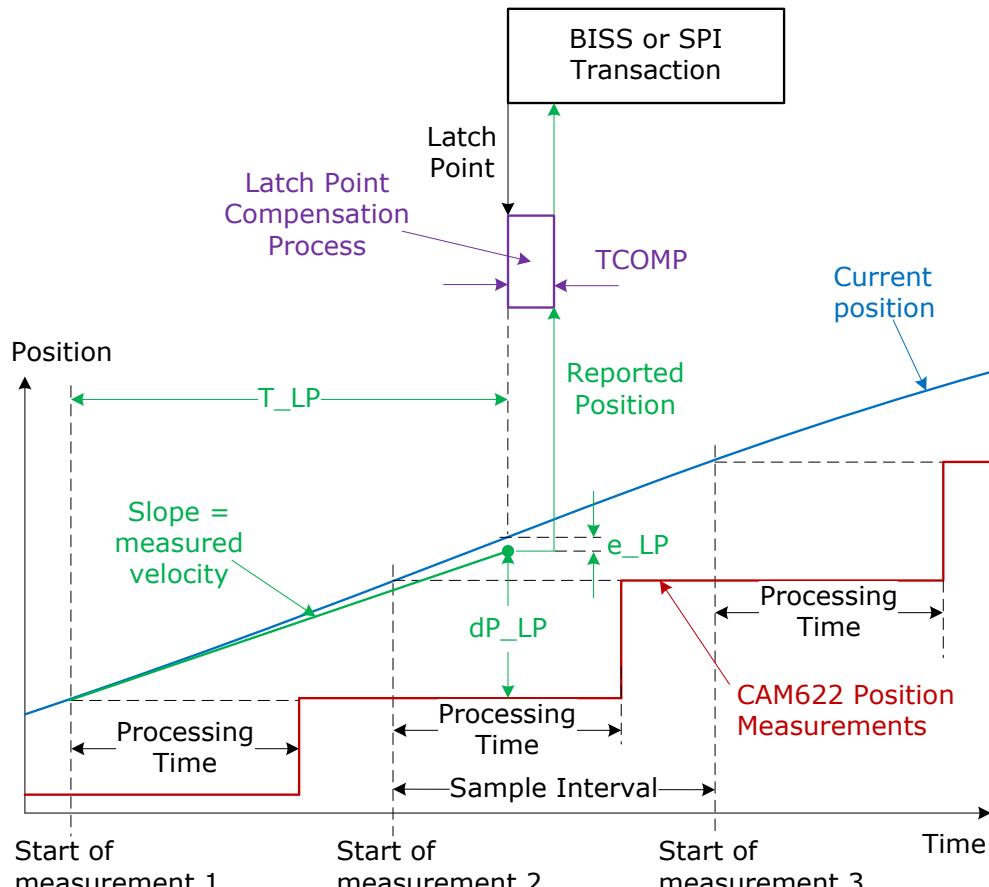

Position measurements are processed by a Motion Filter. This can reduce measurement noise at the expense of a delayed response to changes in velocity. It also corrects for the small position lag between physical angle and each position update. Please see section 13 for full details of how to configure this filter, and its dynamic performance.

### 1.3 Interface Processor Description

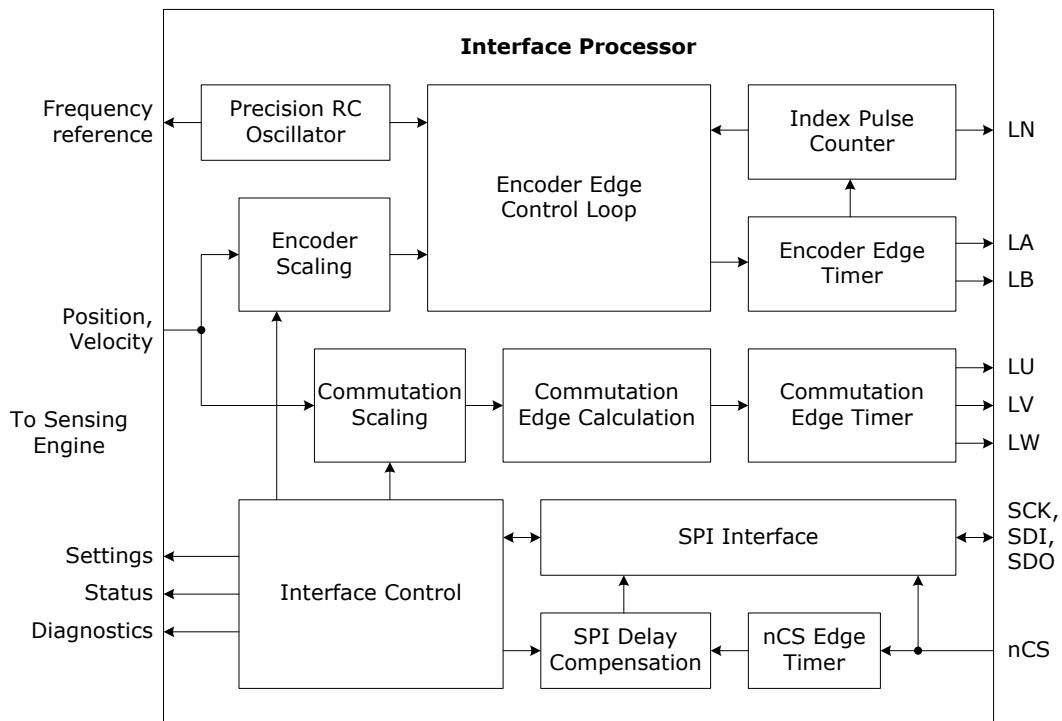

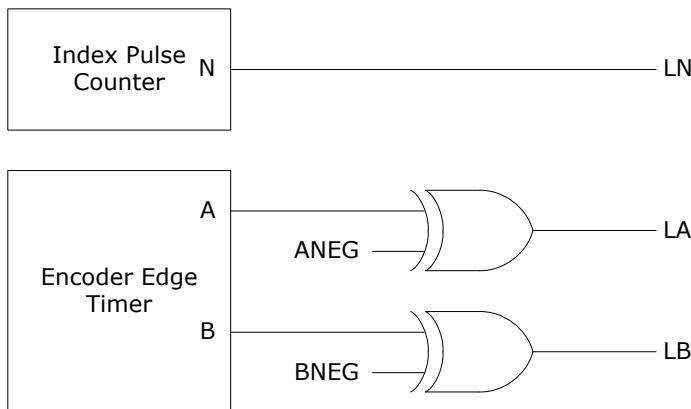

**Figure 5 Interface Processor block diagram**

The Interface Processor communicates measurement results to the outside world. It can generate ABN signals emulating the outputs of an optical encoder. It can also emulate the output of a BLDC motor's Hall sensors used for commutation at the same time.

Encoder signal settings include the number of AB cycles per revolution and the angular position of the N pulse. Commutation signal settings include the number of pole pairs per revolution and an angle offset. These settings are stored in non-volatile memory. Since they are software settings and not a function of hardware, this allows a single hardware variant to address multiple applications. It allows settings to be configured, adjusted or uploaded in the field under software control.

The Interface Processor also includes an SPI interface. This may be used as a primary interface to a host device in place of encoder and commutation signals. Alternatively it may be used to program the CAM622's non-volatile memory to configure sensing, encoder and commutation settings.

When operating as the primary interface, the exact time of the start of each SPI transaction (nCS low) is measured with a timer. This is used to correct for variable delays between Sensing Engine results and SPI, so that position values reported over SPI reflect the exact position when nCS went low.

The Interface Processor shares a Precision RC oscillator frequency reference with the Sensing Engine. Its frequency tolerance affects the scaling of velocity measurements reported by the Sensing Engine and over SPI. However this tolerance does not affect the frequency of encoder signals. If the Precision RC oscillator's frequency is high then the velocity measurement will be low, and this will be exactly compensated by a higher ABN and UVW edge frequency.

## 1.4 Pin Functions

Table 1 summarises CAM622 pin functions and type. Please refer to section 2 for electrical characteristics for each type. Signal directions are given from the CAM622 chip's perspective.

**Table 1 CAM622 pin names and functions**

| Signal Name              | Type                          | Function                                                                                                                                                                                                                        |

|--------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD1, VDD2               | Power                         | Positive supply voltage, internally connected.                                                                                                                                                                                  |

| AVDD                     | Analog Input                  | Analog supply voltage, connect to VDD.                                                                                                                                                                                          |

| VSS, AVSS                | Power                         | 0V connection and common return for sensor inputs.                                                                                                                                                                              |

| nRESET                   | Digital Input                 | Hardware reset, active low.                                                                                                                                                                                                     |

| nCS                      | Digital Input                 | SPI Interface line: Chip Select, active low.                                                                                                                                                                                    |

| SCK                      | Digital Input                 | SPI Interface line: Serial Clock. Serial data is shifted out on the falling edge and captured on the rising edge of SCK.                                                                                                        |

| SDI                      | Digital Input                 | SPI Interface line: Serial Data In. Data is captured on the rising edge of SCK.                                                                                                                                                 |

| SDO                      | Digital and Open Drain Output | SPI Interface line: Serial Data Out. SDO is driven as a digital output by the CAM622 during SPI transactions, when is nCS is low (active). When nCS is high it is Open Drain to allow other slave devices to share the SPI bus. |

| SI                       | Digital or open drain output  | Sample indicator indicating new results or for controlling an LED.                                                                                                                                                              |

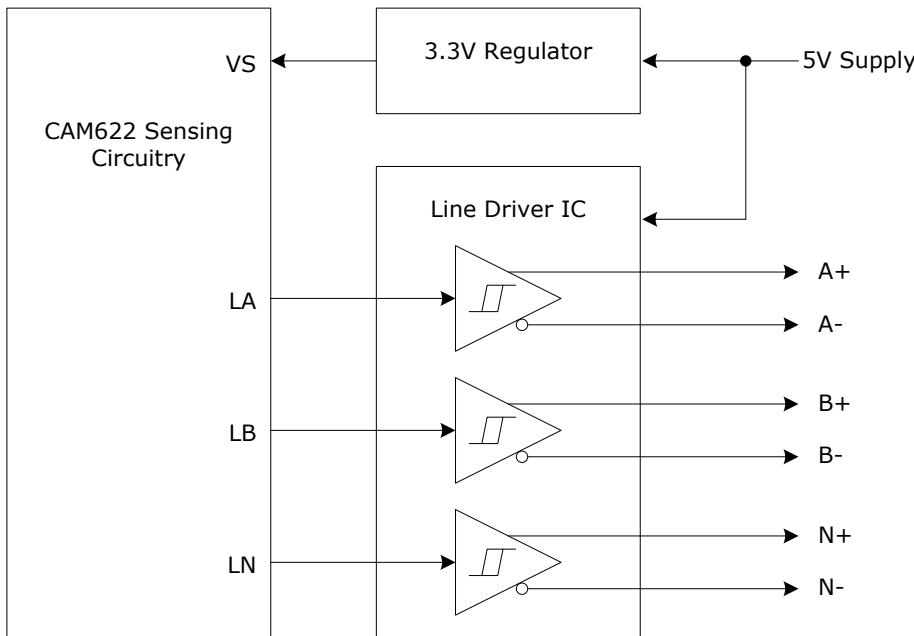

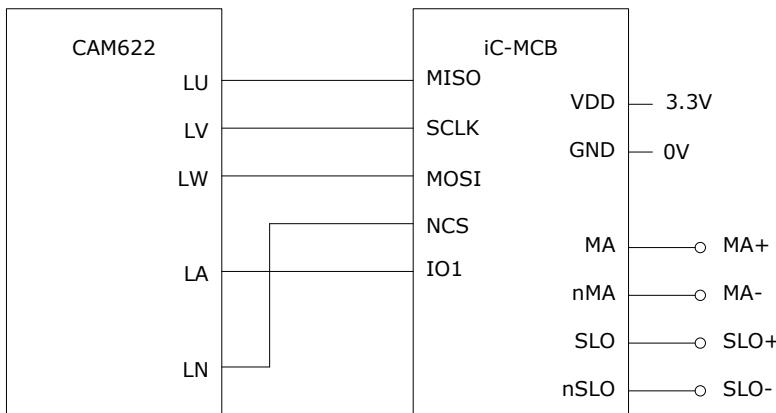

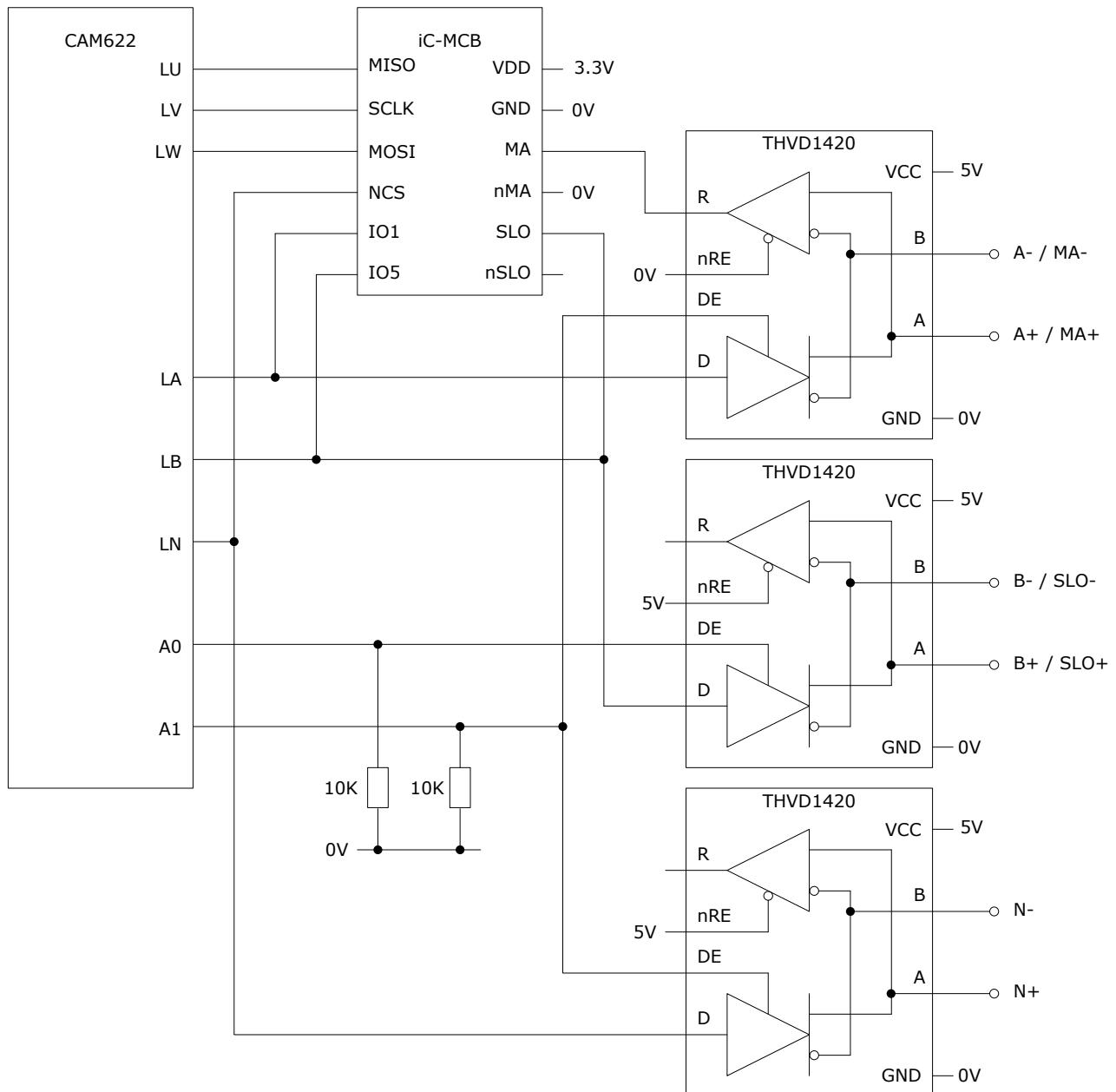

| LA, LB, LN               | Digital Outputs               | Encoder outputs, single ended, logic level. Use an external line driver to generate RS-422 level ABN signals from these, see section 9.5. Also used as control signals for BiSS operation, see section 10.3                     |

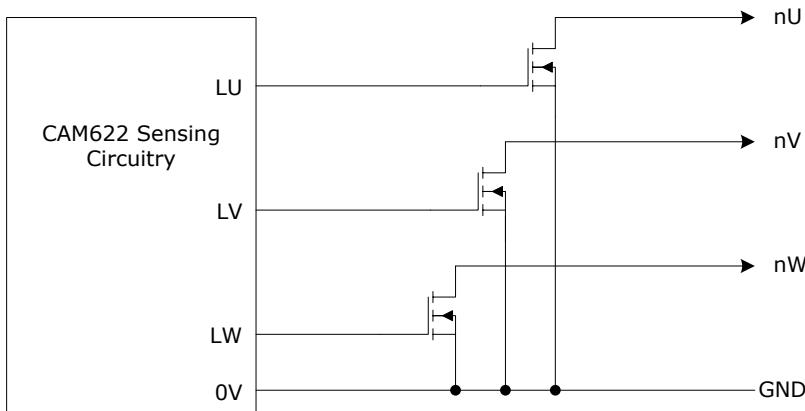

| LU, LV, LW               | Digital Outputs               | Motor commutation outputs, single ended, logic level. Use external MOSFETs to generate open drain UVW signals from these, see section 12.2. Also used as control signals for BiSS operation, see section 10.3                   |

| EXT                      | Digital Output                | Configurable function                                                                                                                                                                                                           |

| DR1 – DR3                | Digital Outputs               | Used to drive external MOSFETs for powering the excitation coil of the resonant inductive position sensor.                                                                                                                      |

| COS1, COS2<br>SIN1, SIN2 | Analog Inputs                 | Used to sense the sensor coil outputs of resonant inductive sensors.                                                                                                                                                            |

| A0, A1                   | Digital Outputs               | Configuration outputs, see section 6.8.                                                                                                                                                                                         |

| Exposed Pad              | Shield                        | Centre Pad under package, connect to VSS.                                                                                                                                                                                       |

## 2 Electrical Characteristics

### 2.1 Operating Characteristics

Table 2 Operating characteristics

| Item                             | Min    | Max    | Comments                                                                                 |

|----------------------------------|--------|--------|------------------------------------------------------------------------------------------|

| Operating Supply Voltage VS      | 3.1V   | 3.60V  | VDD, AVDD must be greater than 3.0V                                                      |

| Operating Temperature (ambient)  | -40 °C | 125 °C |                                                                                          |

| VS start voltage relative to VSS |        | 0V     |                                                                                          |

| VS rise rate relative to VSS     | 1V/ms  | 40V/ms | For reliable power on reset, and to avoid more than 0.3V difference between VDD and AVDD |

### 2.2 Absolute Maximum Ratings

Table 3 Absolute maximum ratings

| Item                                     | Max                 |

|------------------------------------------|---------------------|

| Voltage between VDD or AVDD and VSS      | -0.3V to +4.0V      |

| Voltage on any other pin relative to VSS | -0.3V to (VDD+0.3V) |

| Current into or out of Digital Output    | 4mA                 |

### 2.3 Digital Input Specifications

Table 4 Digital input specifications

| Item                  | Min       | Max       |

|-----------------------|-----------|-----------|

| Input Low             | VSS       | 0.2 x VDD |

| Input High            | 0.8 x VDD | VDD       |

| Input leakage current |           | ±2µA      |

### 2.4 Digital Output Specifications

Table 5 Digital output specifications

| Item                | Min  | Max  | Comments            |

|---------------------|------|------|---------------------|

| Output Low Voltage  |      | 0.4V | IOL = 4mA           |

| Output High Voltage | 2.4V |      | VDD=3.3V IOH = -4mA |

### 2.5 Application Memory Characteristics

Table 6 Application Memory characteristics

| Item                                      | Min      | Max  | Comments                                                  |

|-------------------------------------------|----------|------|-----------------------------------------------------------|

| Number of non-volatile memory updates     |          | 5000 | Across Operating Supply Voltage and Operating Temperature |

| Characteristic retention, -40°C to +125°C | 20 years |      |                                                           |

### 2.6 Hardware Reset

The CAM622 chip will be reset when the host device pulls nRST low. The timing parameter TnRSTL is the low time for the nRST signal, and this is specified in Table 7.

Table 7 Reset timing

| Parameter | Description                                         | Min    |

|-----------|-----------------------------------------------------|--------|

| TnRSTL    | Duration of nRESET pin low to reliably reset CAM622 | 2.5 µs |

### 3 External Circuitry

Sections 3.1 and 3.2 detail the circuitry for processing sensor signals using the CAM622. This is all that is needed when the host communicates with the CAM622 chip over SPI.

#### 3.1 Schematic, Sensing Circuitry

Figure 6 is a schematic for circuitry required around the CAM622 chip for its sensing function.

**Figure 6 CAM622 external circuitry schematic**

Sensors with a Subtype of 0 only have one pair of sensor coils COS and SIN, which are connected to the COSA and SINA nets. They do not use COSB and SINB connections. In this case R\_MB, C\_MB, R\_FB and C\_FB may be omitted.

### 3.2 Components Required, Sensing Circuitry

Table 8 lists the component values required for the schematic of Figure 6.

**Table 8 Components required**

| Circuit Ref      | Value, Type        | Tolerance |         | Number required |

|------------------|--------------------|-----------|---------|-----------------|

|                  |                    | Grade A   | Grade B |                 |

| R_RP, R_CS       | 10kΩ               | ±5%       |         | 2               |

| R_RS             | 470 Ω              | ±5%       |         | 1               |

| R_VDD, R_AVDD    | 0.68Ω              | ±5%       |         | 2               |

| R_EX             | 10Ω                | ±5%       |         | 1               |

| R_DRL, R_N       | 220Ω               | ±5%       |         | 2               |

| R_DRH            | 120Ω               | ±5%       |         | 2               |

| R_TO             | 1MΩ                | ±5%       |         | 1               |

| R_MA, R_FA       | 150Ω               | ±0.1%     | ±1%     | 4               |

| R_MB, R_FB (1)   | 150Ω               | ±1%       |         | 2               |

| C_S1, C_S2, C_S3 | 100nF              | ±10%      |         | 3               |

| C_S4             | 22μF, ESR < 0.05 Ω | ±20%      |         | 1               |

| C_S5, C_EX       | 10μF, ESR < 0.05 Ω | ±20%      |         | 2               |

| C_R              | 1nF                | ±10%      |         | 1               |

| C_N              | 3.3nF NPO/COG      | ±5%       |         | 1               |

| C_MA, C_FA       | 220pF NPO/COG      | ±1%       | ±5%     | 4               |

| C_MB, C_FB (1)   | 220pF NPO/COG      | ±5%       |         | 4               |

| C_B              | 1μF, ESR < 0.1 Ω   | ±10%      |         | 1               |

| Q1, Q2           | Si1016CX           |           |         | 2               |

| U1               | CAM622             |           |         | 1               |

Note(1): May be omitted when the sensor's Subtype is 0.

Table 9 illustrates the effect of component grade choice on reproducibility error, see also section 3.6.

**Table 9 Reproducibility error due to filter components, 360°rotary sensor**

| Subtype | Grade A | Grade B |

|---------|---------|---------|

| 0       | ±0.14°  | ±0.72°  |

| 3       | ±0.05°  | ±0.24°  |

| 5       | ±0.03°  | ±0.14°  |

| 7       | ±0.02°  | ±0.1°   |

| 9       | ±0.016° | ±0.08°  |

### 3.3 Supply and Reset Circuitry

The circuitry is powered by the VS connection.

R\_VDD and C\_S4 form an RC filter, which limits the amount of supply ripple on VS that reaches the CAM622's VDD pin. R\_AVDD and C\_S5 form another RC filter which further reduces ripple on the AVDD. It is essential that the voltage magnitude between the VDD and AVDD pins remains below 0.3V, including when supply voltage is applied to and removed from VS. This condition is met with the component values specified, and providing the maximum VS rise rate specified in Table 2 is respected.

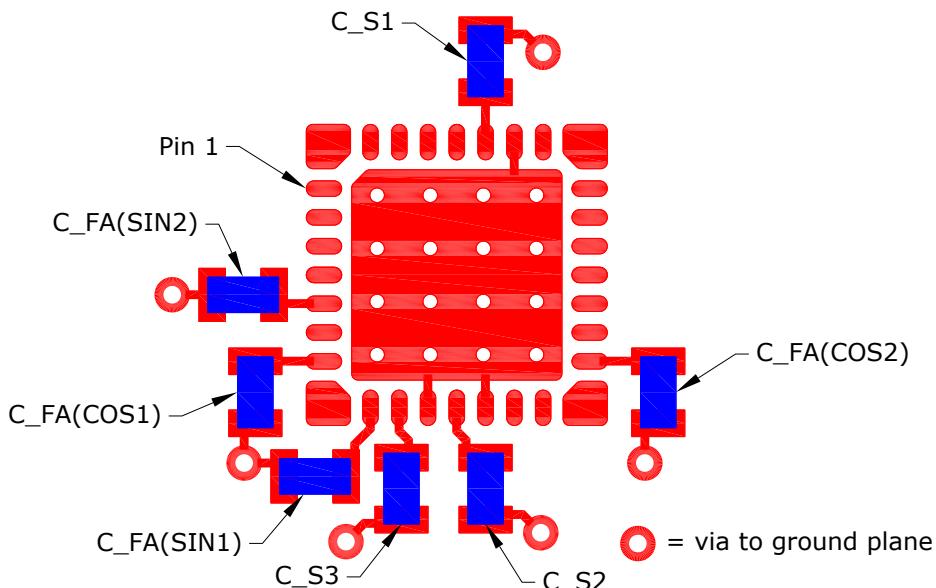

Decoupling capacitors C\_S1, C\_S2 and C\_S3 must be positioned immediately next to the CAM622 chip with short connections to it. Please see Figure 9 for the recommended layout and wiring of these components.

Reset circuitry connects to the CAM622 chip's nRESET pin. C\_R and R\_RP ensure nRESET is initially low and then high if nRST is not connected to a host device, to ensure the part resets when power is first applied. nRST is an optional connection to the host device. It can simplify updates to internal software over SPI.

### 3.4 Excitation Circuitry

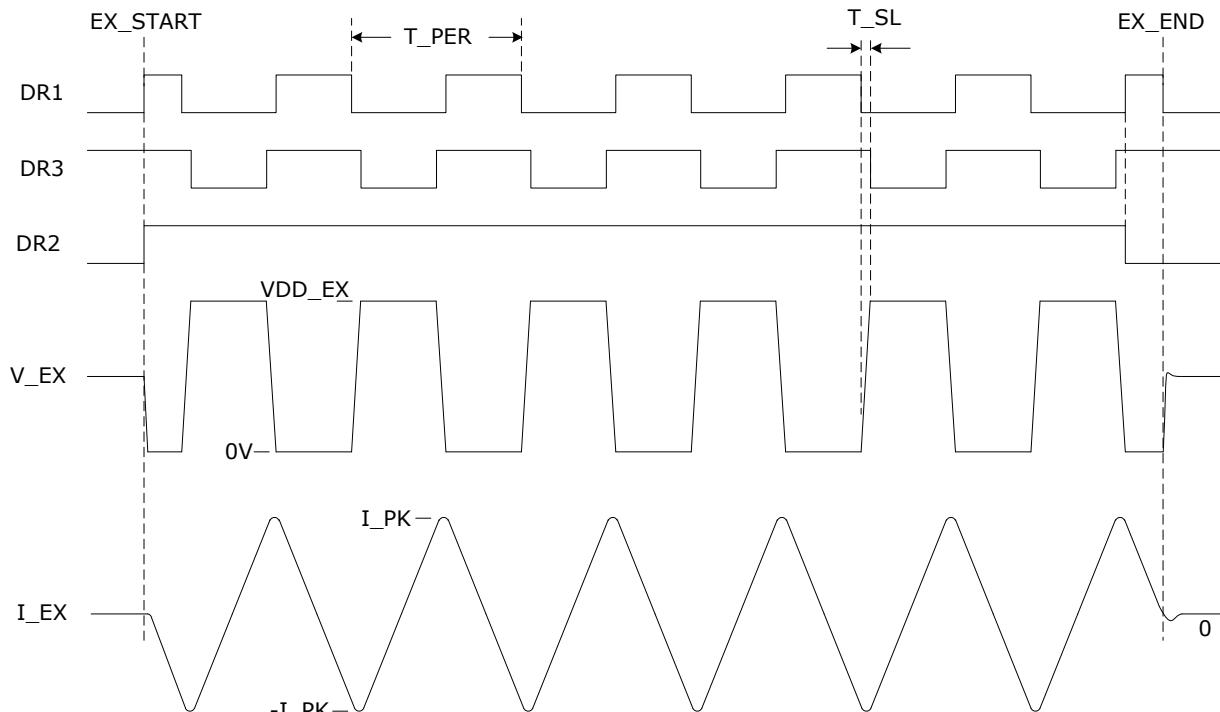

The sensor is powered by excitation current into its excitation connection EX. Excitation comprises a few cycles of alternating current. This flows between the start and end of excitation, marked EX\_START and EX\_END in the waveform drawing of Figure 7.

Excitation current has period  $T_{PER}$  marked in the waveforms of Figure 7, and hence frequency  $1/T_{PER}$ . The CAM622 chip adjusts this period so that the excitation frequency matches the target's resonant frequency.

Excitation current comes from MOSFET Q1. This includes n-channel and p-channel devices Q1A and Q1B respectively, which form a half bridge driver. Their gates are controlled by the CAM622 with non-overlapping signals DR1 and DR3. There is a time delay  $T_{SL}$  between each MOSFET turning off and the next turning on, and this yields high efficiency.

**Figure 7 Excitation waveforms**

MOSFET Q2A is controlled by DR2 and is on during excitation. This connects capacitor  $C_N$  between EX and 0V, so that it conducts excitation coil current when Q1A and Q1B are both off. During this period the excitation current will be approximately constant because the excitation coil is an inductive load. The voltage at EX will therefore slope up or down at a controlled rate. This makes the EX output a trapezoidal waveform approximating a sine wave, to minimise unwanted emissions.

Excitation ends at EX\_END, marked in Figure 7, and is followed by resonator detection. At this point Q1A, Q1B and Q2A are all turned off in order to minimise any residual current flowing in the excitation coil during resonator detection, which would otherwise disturb measurements. This is of great benefit to performance, and is one distinguishing feature of resonant inductive sensing compared to conventional (non-resonant) inductive sensing. Conventional inductive sensing requires excitation during detection, so there is no opportunity to switch off the excitation current completely.

MOSFETs are driven by resistors  $R_{DRH}$  and  $R_{DRL}$ . These ensure MOSFETs switch on and off slowly, to avoid unwanted transients during and immediately after excitation.

Resistor  $R_N$  helps to absorb any remaining transients in the transition from excitation to detection after EX\_END. It is switched into circuit by Q2B, and is also controlled by the DR2.

### 3.5 Sensor Signal Description

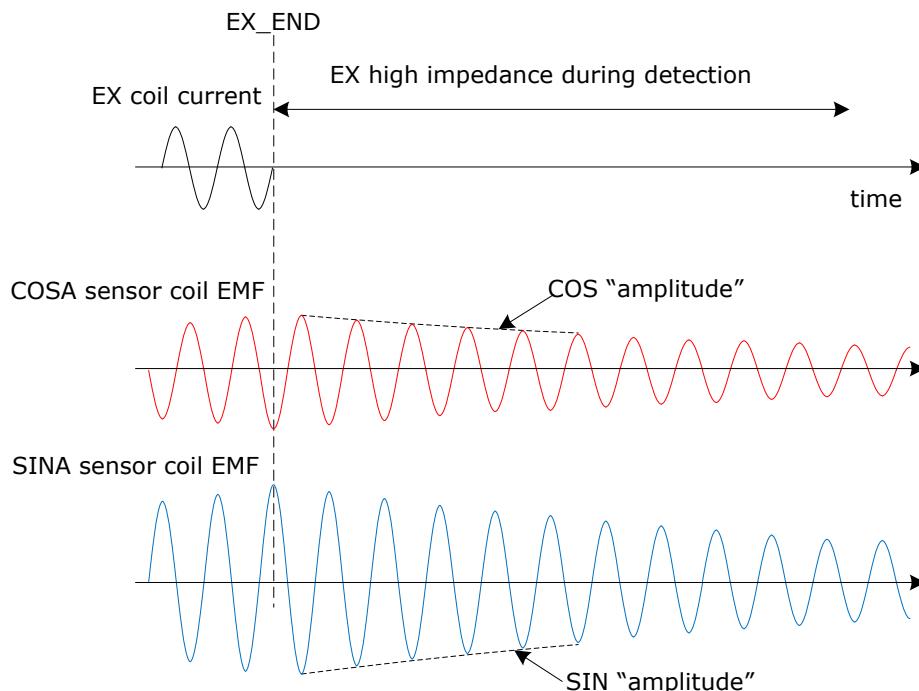

The excitation current  $I_{EX}$  illustrated in Figure 7 is applied to the sensor's excitation coil. This couples to the moving target's resonator and causes it to resonate. The resonance builds up while  $I_{EX}$  is applied, and starts to decay when it is removed at  $EX\_END$ . The decay takes many cycles because the resonator is designed to have a high Q-factor.

The resonator couples back into the sensor's sensor coils. These are patterned so that the coupling between the resonator and sensor coils varies sinusoidally with angle. Coupling to the fine sensor coils COSA and SINA repeats multiple times per target rotation. The number of sinusoidal repeats depends on the sensor design and equals its Subtype. Coupling to the coarse sensor coils COSB and SINB repeats once per rotation. If a sensor's Subtype equals 0 then it only has one pair of sensor coils COS and SIN.

Figure 8 illustrates the end of the excitation current waveform and the resulting resonator signals induced in the fine sensor coils. Coarse sensor signals are similar but are typically smaller.

**Figure 8 Sensor coil signals COSA and SINA**

To determine the angle of the moving target, the CAM622 detects the amplitude of each sensor signal. This is illustrated as the envelope of the waveform in Figure 8 for simplicity. Please refer to the Type B Sensor Reference Manual for more details.

### 3.6 Sensor Signal Filtering

An external low-pass filter is required to suppress any high-frequency interference coupled into the sensor and its connections. This comprises two stages of RC filtering per sensor signal. This simple approach is ensures gain and phase matching across channels, which is important for accuracy.

Close tolerance filter component values are preferred when accuracy is particularly important, denoted "Grade A" in Table 8. The contribution made by the filter to reproducibility error depends on grade as illustrated in Table 9.

### 3.7 Interface Circuitry for Other Interfaces

The circuitry described above is required for all interfaces. It is typically sufficient when the CAM622 is interfaced over its SPI interface to a host device on the same PCB.

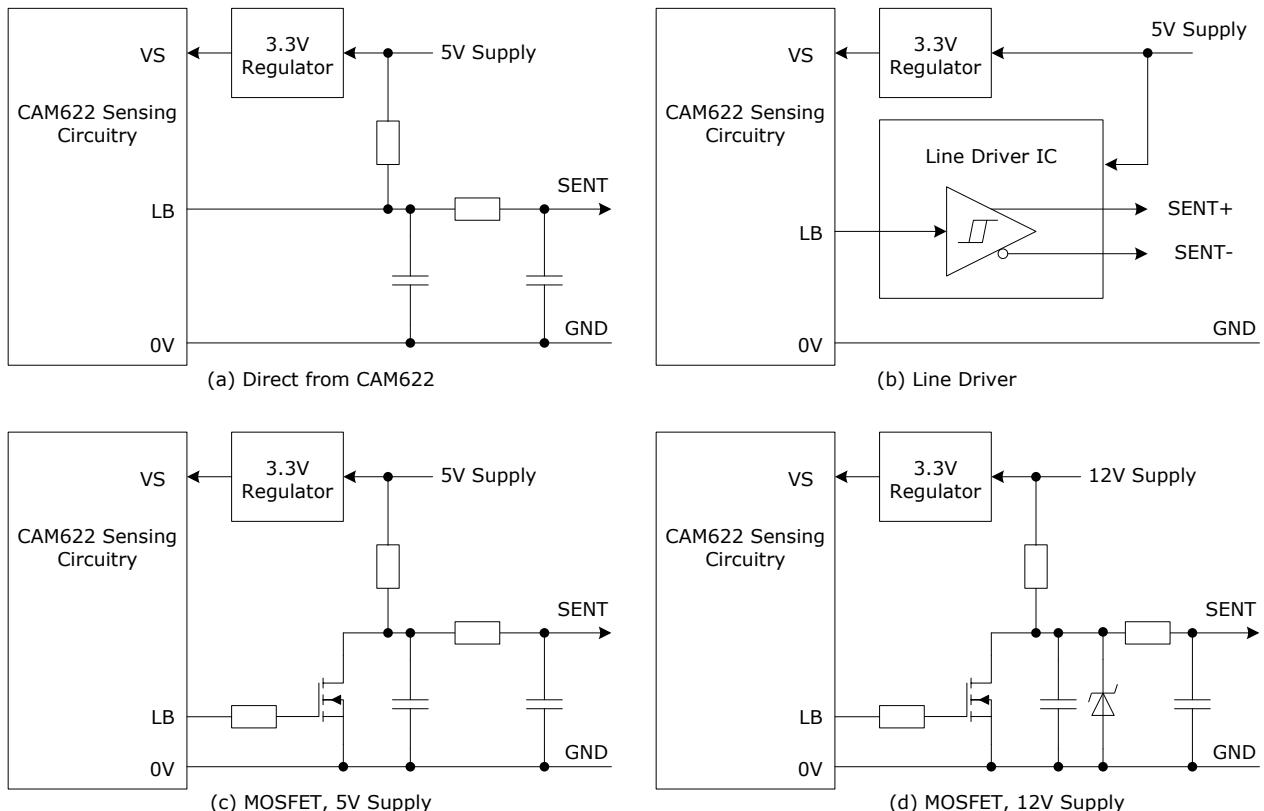

For applications where encoder outputs are the primary interface it is likely that line drivers will also be required. These boost current and voltage, provide line matching and add differential outputs. Please refer to section 9.5.

Where BiSS is the primary interface, or used to configure ABN operation, the circuitry described in section 10.3 will be required.

Where SENT is the primary interface, signal conditioning options are described in section 11.4.

Motor commutation outputs LU, LV and LW will usually require external MOSFETs to interface to a motor controller, see section 12.2.

### 3.8 Layout Recommendations

It is recommended to use a PCB with at least 4 layers. A middle layer should include a solid ground plane underneath the CAM622 and the circuitry of Figure 6.

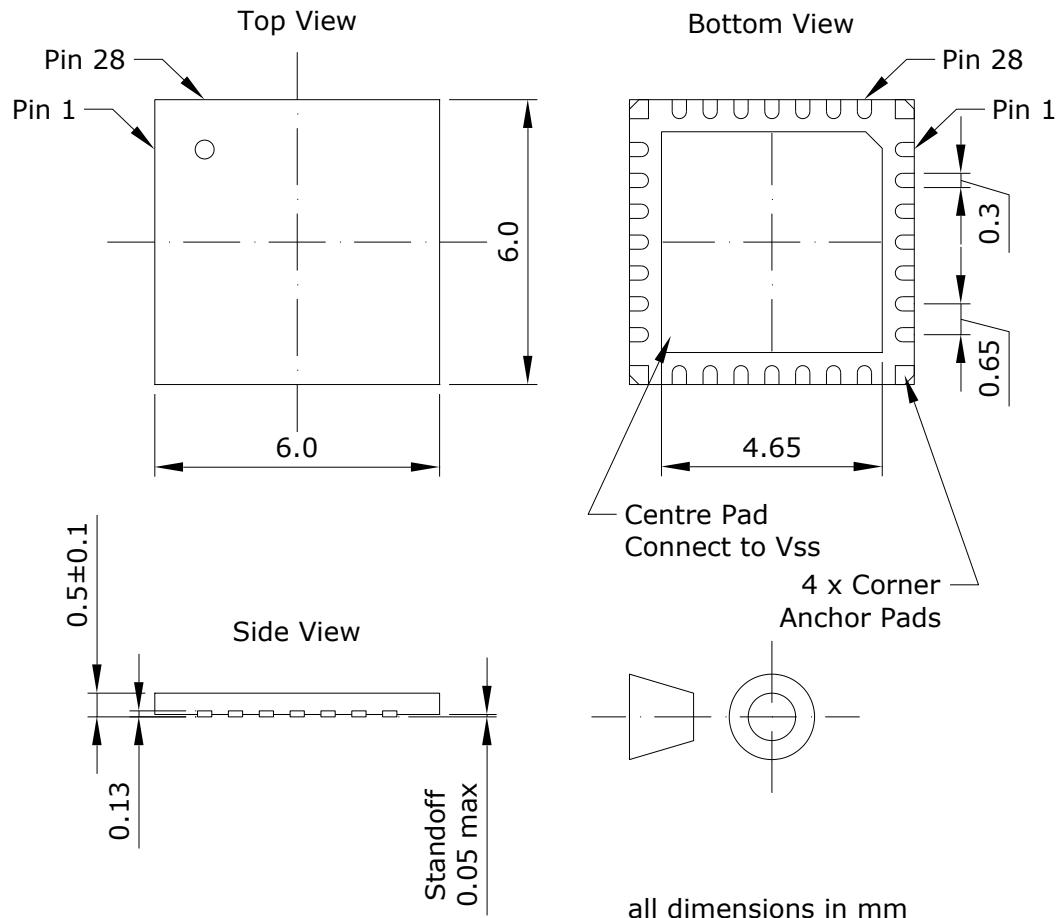

Figure 51 shows the recommended footprint for the CAM622 part. This includes a large centre pad. It is recommended to add vias to this centre pad as shown in the footprint drawing. These are denoted "thermal vias" in Figure 51. They also serve to maintain a low impedance connection between the ground plane and the centre pad. Having a grounded centre pad also allows short and direct connections to the VSS pins, which is important for performance.

Decoupling capacitors C\_S1, CS2 and C\_S3 and filter capacitors C\_FA and C\_FB must be positioned immediately adjacent to the CAM622 chip. Their grounded end must be connected directly to the ground plane or an immediately adjacent pin connected to VSS or AVSS.

Figure 9 illustrates the recommended arrangement.

**Figure 9 Recommended capacitor locations and wiring**

Connections to the CAM622 chip's other pins are less critical.

### 3.9 Sensor Coil and Filter Network Connections

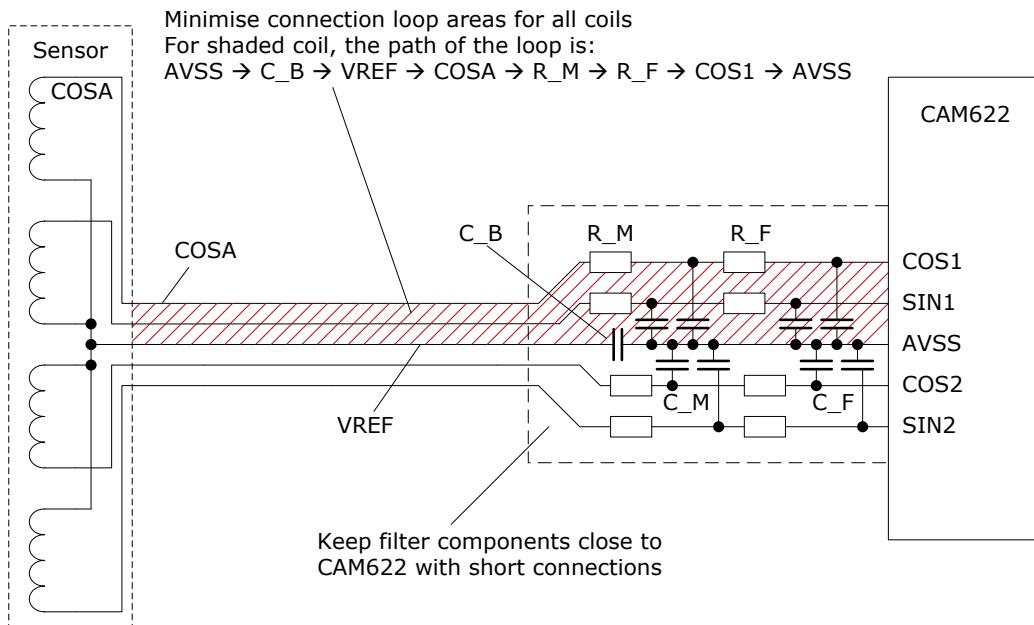

Figure 10 illustrates connections between sensor coils and the CAM622 circuit, including its filter components. When a sensor coil is connected to the CAM622 circuit, the traces and/or wires forming the connection make a loop. The loop formed by the COSA coil connection is shaded as an example. The loop area for each of the sensor coils must be minimised, in order to minimise coupling to the target and/or any AC magnetic interference.

**Figure 10 Sensor coil and filter connections to CAM622**

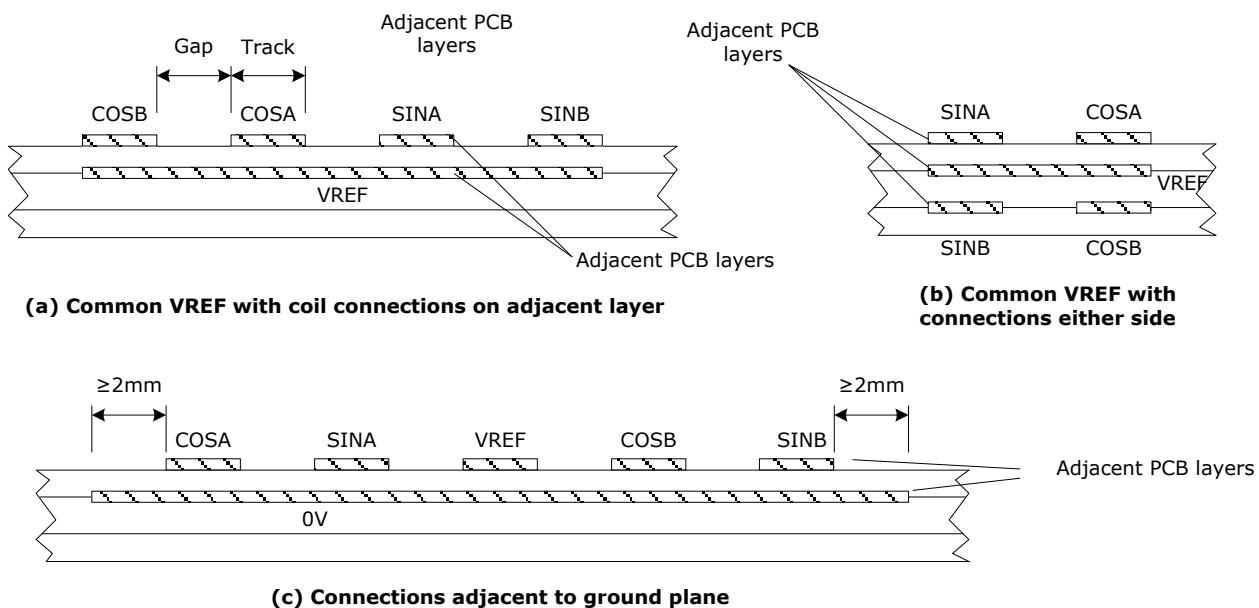

Wires used for connection must be run in a tight bundle, on adjacent conductors in a ribbon cable or twisted. Conductors on a PCB should be arranged adjacent to a common VREF conductor as in Figure 11 (a), (b) or (c). These bundles should ideally be less than 100mm long.

**Figure 11 PCB conductor arrangements for sensor coils**

Track and Gap figures should be minimised, providing connection resistance does not fall below  $2\Omega$ , or below  $1\Omega$  for a VREF connection that is common to two or more coils.

### 3.10 Excitation Circuit and Coil Connections

The CAM622 chip drives the gates of external MOSFETs, which in turn drive current into the excitation coil to energise the resonator inside the target.

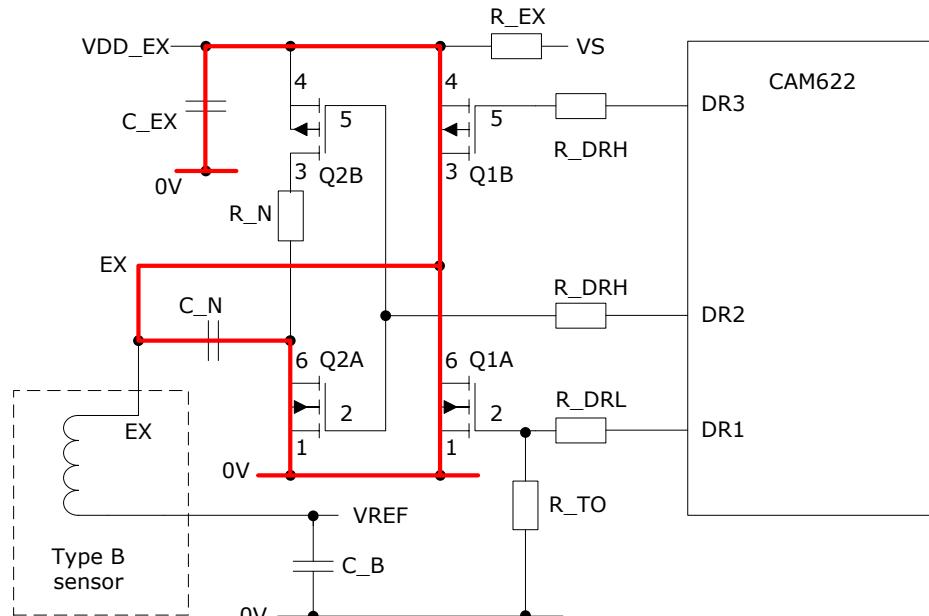

To keep the circuit efficient and to minimise emissions, the traces used to form the current paths highlighted in red in Figure 12 must be kept short, direct and as wide as possible. To achieve this, the relevant components (C\_EX, Q1, Q2, C\_N) must be located together.

**Figure 12 Excitation circuit with critical paths highlighted**

Excitation coil connections must be made with a minimum of loop area, in a similar way to sensor coil connections.

The traces connecting the excitation coil (EX and VREF nets) should be at least 0.2mm wide and ideally less than 50mm long.

## 4 Resonator Detection

Type B sensors detect the position of an electrical resonator inside a moving target. Table 10 lists parameters relevant to the CAM622 chip's detection of resonators, and their values.

**Table 10 Resonator Detection Specifications**

| Parameter                                                                         | Value     | Comment                                                                                                                                   |

|-----------------------------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Nominal Resonator Centre Frequency                                                | 833.3kHz  | For a reported relative frequency of 0Hz with a nominal CAM622 chip                                                                       |

| CAM622 Frequency tolerance across parts and Operating Temperature                 | $\pm 3\%$ | Tolerance of the CAM622's oscillator, and hence tolerance of the Nominal Resonator Centre Frequency and Sample Interval. See section 6.5. |

| Resonator tuning range Relative to Nominal Resonator Centre Frequency             | $\pm 8\%$ | For the CAM622 to report VALID Across Operating Temperature Range -40°C to +125°C                                                         |

| Recommended resonator tuning range Relative to Nominal Resonator Centre Frequency | $\pm 5\%$ | For best Amplitude and hence resolution                                                                                                   |

| Minimum Resonator Q-factor                                                        | 12        | For the CAM622 to report VALID                                                                                                            |

| Minimum Amplitude (AMPA, Table 13)                                                | 3000      | Recommended minimum for design purposes                                                                                                   |

|                                                                                   | 1000      | Absolute minimum to report VALID                                                                                                          |

Please refer to the Type B Sensor Reference Manual for details, including how to tune the target's resonator to match the CAM622 Resonant Inductive Encoder IC.

## 5 SPI Hardware

### 5.1 Overview

This section describes how the CAM622 and a host exchange data over an SPI interface.

### 5.2 Data Transfer Method

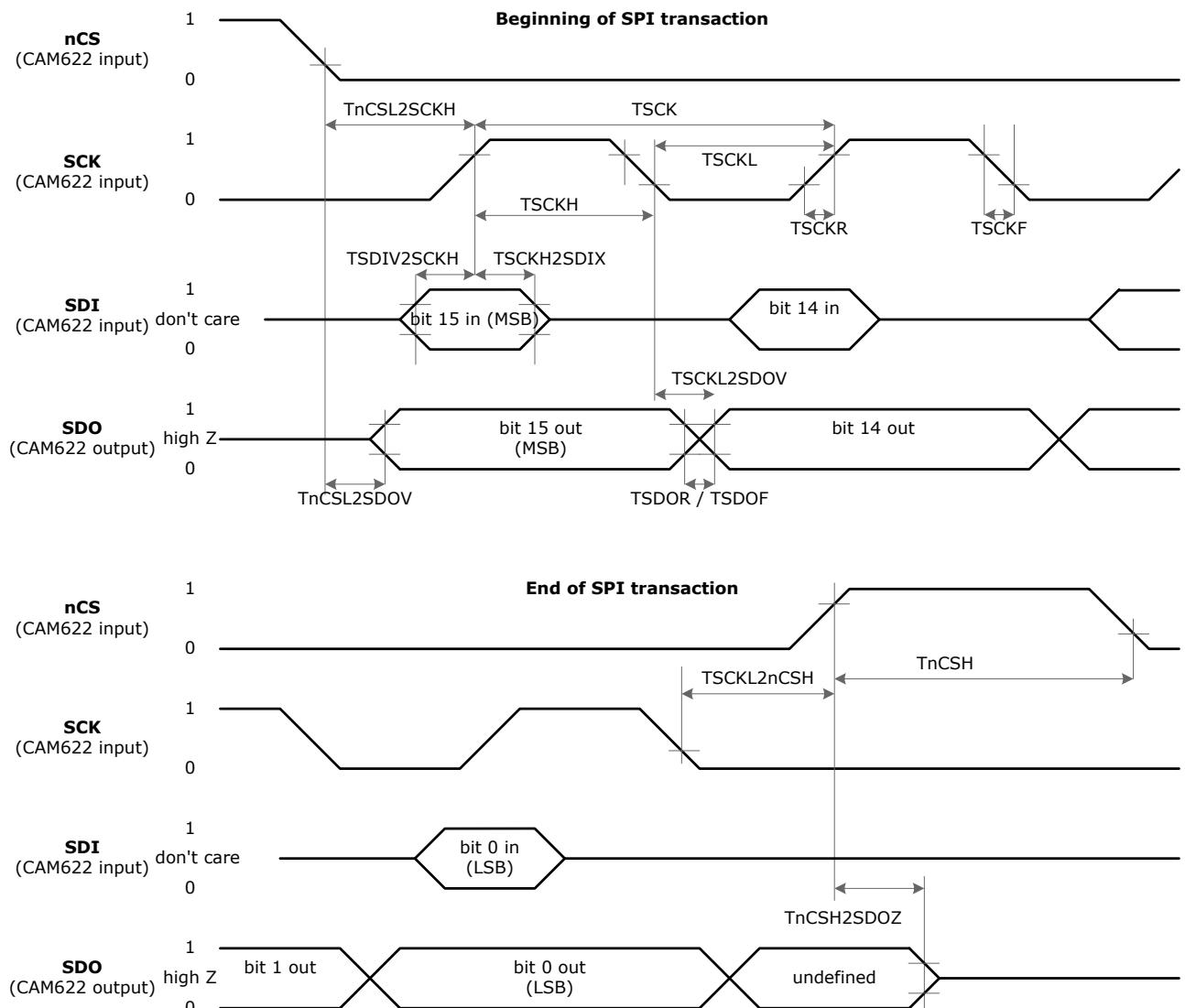

The CAM622 chip is an SPI peripheral. The host controls the nCS, SCK and SDI inputs to the CAM622. The host starts a data transfer by driving nCS low. It sends data to the CAM622 with the SDI line, and provides the CAM622 with a serial clock line SCK. The CAM622 detects each SDI bit on the rising edge of SCK. The CAM622 sends data back to the host with the SDO line. SDO changes state on the falling edge of SCK. The host should detect the state of SDO on each rising edge. This is commonly referred to as SPI Mode 0. The beginning and end of an SPI transaction are illustrated in Figure 13.

**Figure 13 SPI Data Transfer**

The timing parameter marked TnCSH is the time that nCS remains high between successive SPI transactions. Its minimum value depends on the details of the preceding SPI transaction. Several values are given in Table 11. For example TnCSH\_read is the time between read operations when ABEN=0, as illustrated in Figure 18.

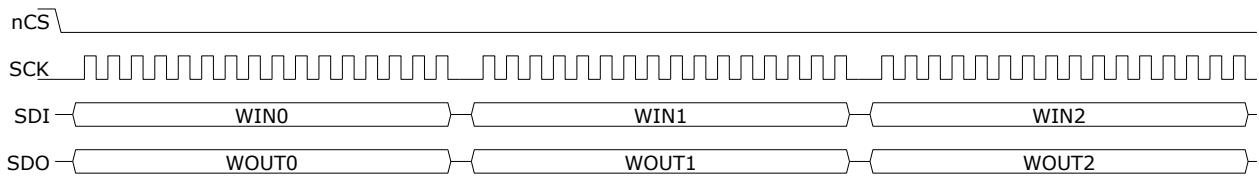

Data is transmitted most significant bit (MSB) first. The CAM622 interprets data it receives on SDI as 16-bit words. This data is denoted WIN0, WIN1, WIN2 in Figure 14. The host should also interpret data output by the CAM622 as 16-bit words, denoted WOUT0, WOUT1, WOUT2.

**Figure 14 Arrangement of SPI words**

All SPI transactions MUST be bounded by chip select (nCS) being driven low at the start and being driven high at the end. The SPI interface will not function if nCS remains permanently low.

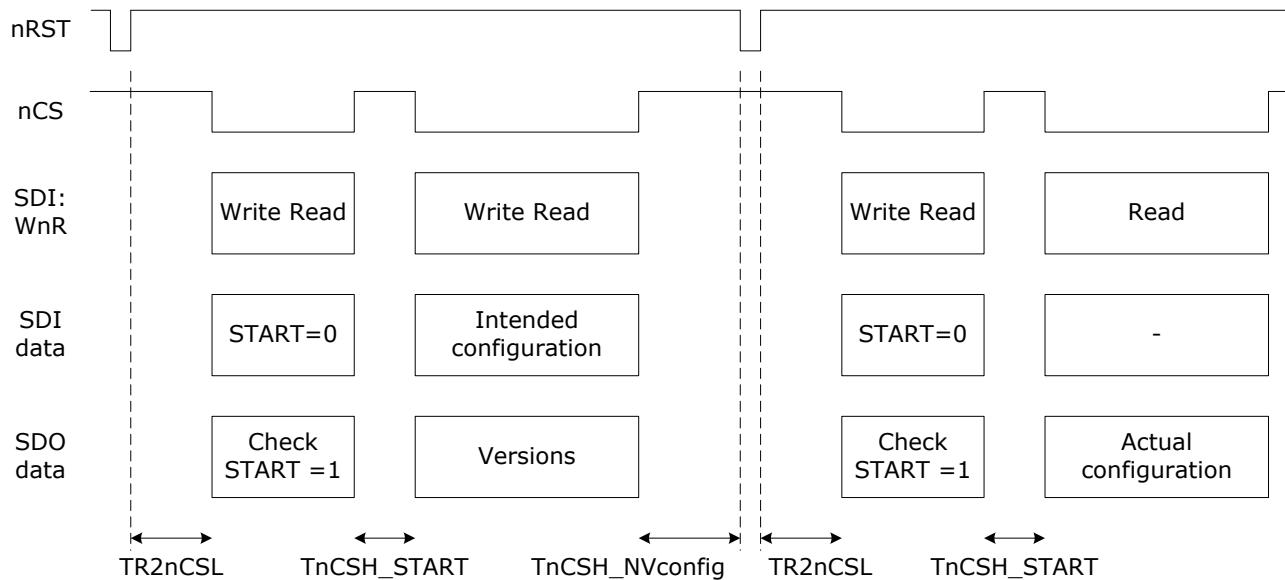

### 5.3 SPI Following Reset

The CAM622 includes power on reset circuitry that holds it in reset until its power supply has reached a level suitable for normal operation. It may also be reset by pulling nRESET low, or by setting the RESET bit (section 6.8).

Once out of reset, the CAM622 performs an internal self test and validity checking procedure. This process must complete for the CAM622 to subsequently enter its normal operating mode, to allow measurements and register access over SPI. To complete successfully, the host must maintain nCS high during the procedure. The minimum high time TR2nCSL(min) between coming out of reset and nCS low is specified in Table 11.

If the host interrupts self test and validity checking by pulling nCS low, the CAM622 will enter its bootloader mode. Please refer to document "Uploading Application Code" for details of this process.

## 5.4 SPI Transaction Timings

Table 11 specifies the timing parameters required for correct operation of the CAM622 SPI interface.

**Table 11 SPI Transaction Timings**

| Parameter      | Description                                                                  | Min | Max | Units |

|----------------|------------------------------------------------------------------------------|-----|-----|-------|

| TR2nCSL        | Time between coming out of reset and first nCS low                           | 20  | -   | ms    |

| TSCKL          | SCK Input Low Time                                                           | 30  | -   | ns    |

| TSCKH          | SCK Input High Time                                                          | 30  | -   | ns    |

| TSCK           | SCK clock period                                                             | 66  | -   | ns    |

| TSCKR          | SCK Input Rise Time                                                          | -   | 7.5 | ns    |

| TSCKF          | SCK Input Fall Time                                                          | -   | 7.5 | ns    |

| TSDOR          | SDO Rise Time (50pF load)                                                    | -   | 10  | ns    |

| TSDOF          | SDO Fall Time (50pF load)                                                    | -   | 10  | ns    |

| TSDIV2SCKH     | SDI Setup Time                                                               | 30  | -   | ns    |

| TSCKH2SDIX     | SDI Hold Time                                                                | 30  | -   | ns    |

| TnCSL2SDOV     | First SDO state valid after nCS low edge                                     | -   | 50  | ns    |

| TSCKL2SDOV     | SDO state valid after SCK low edge                                           | -   | 20  | ns    |

| TnCSL2SCKH     | nCS low to SCK edge                                                          | 500 | -   | ns    |

| TSCKL2nCSH     | Last SCK edge to nCS high                                                    | 90  | -   | ns    |

| TnCSH2SDOZ     | nCS high to SDO high Z                                                       | -   | 50  | ns    |

| TnCSH_config   | Write-read intended configuration up to and including SICONFIG register      | 20  | -   | μs    |

| TnCSH_read     | Read from any registers, when ABEN=0                                         | 4.0 | -   | μs    |

| TnCSH_ABNread  | Read from any registers, when ABEN=1                                         | 20  | -   | μs    |

| TnCSH_START    | Write-read CTRL register only, following a clearing of START bit with ABEN=1 | 20  | -   | μs    |

|                | Write-read CTRL register only, other                                         | 10  | -   | μs    |

| TnCSH_NVconfig | Write-read standalone configuration and save to non-volatile memory.         | 50  | -   | ms    |

## 6 Register Access and Descriptions

The CAM622 includes a set of registers used to configure its operation. A host may also read version information and the results of measurements from registers.

Registers may be accessed over SPI, see section 6.1. Once configured for BiSS operation, they may also be accessed over BiSS, see sections 10.9 and 10.10.

### 6.1 Register Access over SPI

The host accesses CAM622 registers over the SPI interface, see section 5. Each SPI transaction, the host sends a number of data words to the CAM622 denoted WIN0, WIN1, WIN2... and the CAM622 returns data words to the host denoted WOUT0, WOUT1, WOUT2...

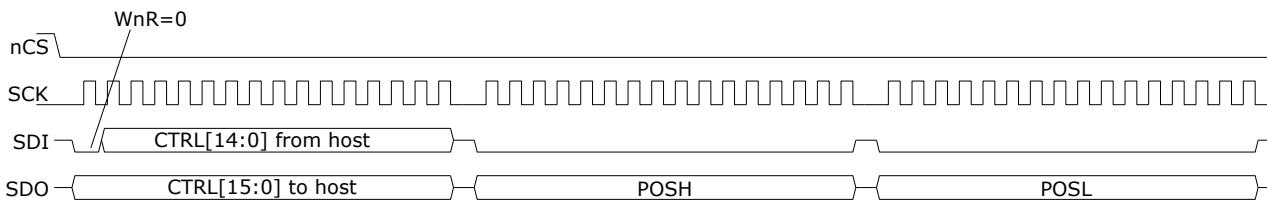

To read registers without modifying their contents, the host must clear the first bit of the first word it sends to the CAM622 (WnR=0, bit 15 of WIN0). The contents of the CAM622's registers are returned in the WOUT words. WOUT0 corresponds to the contents of register address 0x00 (CTRL), WOUT1 corresponds to the contents of register address 0x01 (POSH), and so on. Please see Figure 15. Apart from the WnR bit, the CAM622 ignores all of the WIN words it receives from the host.

**Figure 15 Register read operation**

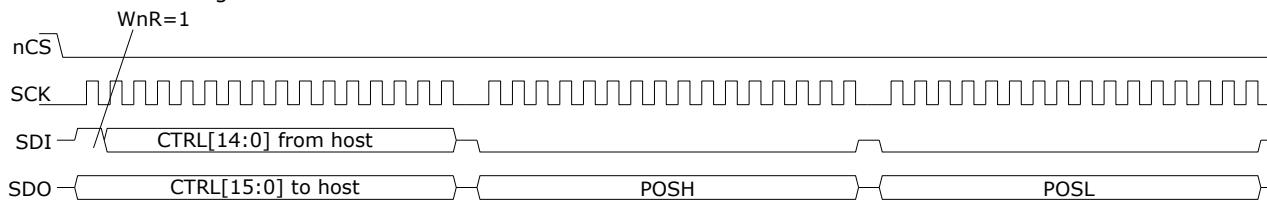

To write new values to registers, the host must set the first bit of the first word it sends to the CAM622 (WnR=1, bit 15 of WIN0). The CAM622's register contents are updated based on the WIN0, WIN1, WIN2... values it receives from the host. WIN0 is written to the register at address 0x00 (CTRL), WIN1 is written to the register at address 0x01, and so on. Please see Figure 16.

**Figure 16 Register write-read operation**

During a write operation, the CAM622 returns register contents in WOUT0, WOUT1, WOUT2... Note these are the contents of the registers as they stood before the SPI transaction. An SPI transaction with the WnR bit set therefore performs both write and read operations, and is referred to below as "write-read".

Register access may be either read only ("R") or write-read ("WR"). The contents of read only registers are only updated by the CAM622. When performing a write-read operation, the host must write 0x0000 to read only registers. The contents of write-read registers are updated by the host, using a write-read SPI transaction.

The control register CTRL is an exception, including bits with both read only and write-read access.

Unimplemented registers and unimplemented bits within registers must be written to 0 when the host performs a write-read operation.

## 6.2 Register Listing

This section provides an overview of registers and their locations. The tables below list register addresses, names, a brief summary of their function and, where necessary, the section number for more details.

**Table 12 Control register (includes write-read and read only fields)**

| Address | Register Name | Function                                          | Section |

|---------|---------------|---------------------------------------------------|---------|

| 0x00    | CTRL          | Various fields for control and status information | 6.3     |

**Table 13 Results registers (read only \*)**

| Address | Register Name | Function                                                          | Section |

|---------|---------------|-------------------------------------------------------------------|---------|

| 0x01    | POSH          | Position measurement, high word                                   | 7.5     |

| 0x02    | POS_L         | Position measurement, low word                                    |         |

| 0x03    | VEL_H         | Velocity measurement, high word                                   |         |

| 0x04    | VEL_L         | Velocity measurement, low word                                    |         |

| 0x05    | AMPA          | Amplitude measurement, fine coils                                 |         |

| 0x06    | AMPB          | Amplitude measurement, coarse coils                               |         |

| 0x07    | BAMISMATCH    | Position mismatch between coarse and fine coils                   |         |

| 0x08    | FNUM          | Resonator frequency measurement                                   |         |

| 0x09    | FILTLVL       | Current value of Motion Filter level setting                      |         |

| 0x0A    | CRC           | Checksum of registers 0x00 to 0x09 inclusive, not yet implemented |         |

(\*) The POSH register is used as a write-read register when programming a CAM622 for autonomous operation. The value 0x0C1C must be written to POSH in order for the SAVE bit (section 6.8) to take effect. See section 0

The 4 Information Registers may be configured to equal any register values from 0x10 (SECONFIG) onwards.

**Table 14 Information registers (read only)**

| Address | Register Name | Function                                               | Section |

|---------|---------------|--------------------------------------------------------|---------|

| 0x0B    | INFO0         | By default equals CAMID (0x0622 for "CAM622")          | 6.10    |

| 0x0C    | INFO1         | By default equals SYSVER (Version of Application Code) |         |

| 0x0D    | INFO2         | By default equals BOOTVER (Version of Bootloader)      |         |

| 0x0E    | INFO3         | By default equals SEVER (Version of Sensing Engine)    |         |

| 0x0F    |               | Unimplemented                                          |         |

**Table 15 Sensing Engine control registers (write-read)**

| Address | Register Name | Function                                   | Section |

|---------|---------------|--------------------------------------------|---------|

| 0x10    | SECONFIG      | Sensing Engine configuration               | 6.4     |

| 0x11    | INTERVAL      | Interval between measurements              | 6.5     |

| 0x12    | FLTLVLS       | Maximum and minimum filter levels          | 6.6     |

| 0x13    | HYAD          | Hysteresis and adaptive filter sensitivity | 6.7     |

| 0x14    |               | Unimplemented                              |         |

| 0x15    |               | Unimplemented                              |         |

| 0x16    |               | Unimplemented                              |         |

**Table 16 System control registers (write-read)**

| Address | Register Name | Function                                 | Section |

|---------|---------------|------------------------------------------|---------|

| 0x17    | SYSCONFIG     | System configuration                     | 6.8     |

| 0x18    | SICONFIG      | Sample indicator control                 | 0       |

| 0x19    | INDEX10       | Controls the contents of INFO0 and INFO1 | 6.10    |

| 0x1A    | INDEX32       | Controls the contents of INFO2 and INFO3 |         |

| 0x1B    |               | Unimplemented                            |         |

**Table 17 Versions registers (read only)**

| Address | Register Name | Function                    | Section |

|---------|---------------|-----------------------------|---------|

| 0x1C    | CAMID         | Returns 0x0622 for "CAM622" |         |

| 0x1D    | SYSVER        | Version of Application Code |         |

| 0x1E    | BOOTVER       | Version of Bootloader       |         |

| 0x1F    | SEVER         | Version of Sensing Engine   |         |

| 0x20    |               | Unimplemented               |         |

| 0x21    |               | Unimplemented               |         |

| 0x22    |               | Unimplemented               |         |

**Table 18 ABN results registers (read only)**

| Address | Register Name | Function                                | Section |

|---------|---------------|-----------------------------------------|---------|

| 0x23    |               | Unimplemented                           |         |

| 0x24    |               | Unimplemented                           |         |

| 0x25    |               | Unimplemented                           |         |

| 0x26    |               | Unimplemented                           |         |

| 0x27    | ABCOUNTH      | Current AB count value, whole counts    |         |

| 0x28    | ABCOUNTL      | Current AB count value, fractional part |         |

**Table 19 ABN control registers (write-read)**

| Address | Register Name | Function                                                            | Section |

|---------|---------------|---------------------------------------------------------------------|---------|

| 0x29    | ABCONFIG      | Fields for controlling ABN signals                                  | 6.11    |

| 0x2A    | MAXABFREQ     | Controls max AB edge frequency, default is the max value 0x8D (141) | 9.8     |

| 0x2B    | NPOS          | Controls position of N signal, default 0x0000                       | 9.6     |

| 0x2C    | ABCYC         | Controls number of AB cycles per revolution, default 0x0000 (16384) | 9.6     |

| 0x2D    |               | Unimplemented                                                       |         |

**Table 20 UVW results registers (read only)**

| Address | Register Name | Function                                    | Section |

|---------|---------------|---------------------------------------------|---------|

| 0x2E    | UVWCOUNTH     | Current UVW state number, whole states      |         |

| 0x2F    | UVWCOUNTL     | Current UVW state number, fractional states |         |

**Table 21 UVW control registers (write-read)**

| Address | Register Name | Function                                              | Section |

|---------|---------------|-------------------------------------------------------|---------|

| 0x30    | UVWCONFIG     | Fields for controlling UVW signals                    | 6.11    |

| 0x31    | UVWPOS        | Controls start position of UVW signals                |         |

| 0x32    | UVWCYC        | Controls number of cycles (pole pairs) of UVW signals |         |

**Table 22 BiSS control registers (write-read)**

| Address | Register Name | Function                                                       | Section  |

|---------|---------------|----------------------------------------------------------------|----------|

| 0x36    | BISSCONFIG    |                                                                | 6.13     |

| 0x38    | BISSKEY1      | Used to secure settings against unauthorised access over BiSS. |          |

| 0x39    | BISSKEY0      |                                                                |          |

| 0x3A    | BISSMID       | Controls the Manufacturer's ID reported over BiSS              | Table 45 |

| 0x3B    | BISSDID2      | Controls the Device ID reported over BiSS                      |          |

| 0x3C    | BISSDID1      |                                                                |          |

| 0x3D    | BISSDID0      |                                                                |          |

| 0x3E    | BISSNUM1      | Controls the Serial Number reported over BiSS                  |          |

| 0x3F    | BISSNUM0      |                                                                |          |

**Table 23 SENT control registers (write-read)**

| Address | Register Name | Function                                                                                                 | Section  |

|---------|---------------|----------------------------------------------------------------------------------------------------------|----------|

| 0x41    | SENTCONFIG1   | Controls SENT signal behaviour and data format                                                           | 6.15     |

| 0x42    | SENTCONFIG2   | Controls SENT timings                                                                                    |          |

| 0x44    | SENTMSG1      | Fixed values returned in diagnostic data that a customer can use for version numbers and serial numbers. | Table 56 |

| 0x45    | SENTMSG2      |                                                                                                          |          |

| 0x46    | SENTMSG3      |                                                                                                          |          |

### 6.3 CTRL Register

The host accesses CTRL with every SPI transaction, because it located at address 0x00 corresponding to the first word of the SPI transaction. Unlike all other registers, some of the bits that the host accesses are different between writes and reads.

Table 24 shows the names of bits within CTRL controlled by data coming from the host on the SDI line (WIN0 in Figure 14). As noted in section 6.1, the top bit (WnR) controls whether the SPI transaction is to read registers (0) or to write-read (1). The contents of subsequent registers (and the START bit) will only be updated if WnR=1. They will remain unaffected if WnR=0.

**Table 24 CTRL register, bits sent from host**

| CTRL   | 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|-----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|-------|

| Field  | WnR | -  | -  | -  | -  | -  | - | - | - | - | - | - | - | - | - | START |

| Access | W   | -  | -  | -  | -  | -  | - | - | - | - | - | - | - | - | - | W     |

Setting the START bit initiates measurements, and clearing it stops measurements. When START=1, the host may only access registers up to and including INFO3 (address 0x0E).

Table 25 shows the names of bits that the host reads from CTRL.

**Table 25 CTRL register, bits sent from CAM622**

| CTRL    | 15         | 14 | 13 | 12 | 11         | 10 | 9 | 8 | 7 | 6 | 5 | 4     | 3 | 2 | 1 | 0     |

|---------|------------|----|----|----|------------|----|---|---|---|---|---|-------|---|---|---|-------|

| Field   | SYSID[3:0] |    |    |    | COUNT[3:0] |    |   |   | - | - | - | VALID | - | - | - | START |

| Access  | R          |    |    |    | R          |    |   |   | - | - | - | R     | - | - | - | R     |

| Default | 0xA        |    |    |    | 0x0        |    |   |   |   |   |   | 0     |   |   |   | 0     |

SYSID is the System ID. When there are multiple devices on an SPI bus, this may be used to check the correct device is responding. Its value may be changed by the host, see section 6.8. The host may also use SYSID as a basic check that communication with the CAM622 is intact, by checking its value against the expected one.

SYSID may also be used as a check for an unexpected reset. The host should change its value when configuring the CAM622. If the host subsequently reads the default SYSID value instead of this new one, a reset has occurred.

COUNT increments each time a measurement is completed. If the host is designed to read the results of each measurement, for example reading results in response to the signal indicator (section 7.4), then COUNT enables the host to check it has not missed results or read the same set again. COUNT increments in a modulo fashion, so the next value after 0xF is 0x0.

The CAM622 reports VALID=1 when the result of the last measurement was valid. This means the target is in range of sensor, its resonator frequency is within the CAM622 resonator tuning range (section 4) and the Motion Filter has initialised (section 13.1).

## 6.4 SECONFIG Register

SECONFIG includes fields for configuring the Sensing Engine.

**Table 26 SECONFIG register**

| SECONFIG | 15  | 14 | 13 | 12 | 11          | 10 | 9 | 8 | 7 | 6 | 5            | 4 | 3 | 2 | 1 | 0 |

|----------|-----|----|----|----|-------------|----|---|---|---|---|--------------|---|---|---|---|---|

| Field    | DDC | -  | -  | -  | ABSSEL[3:0] |    |   |   | - | - | SUBTYPE[5:0] |   |   |   |   |   |

| Access   | WR  | -  | -  | -  | WR          |    |   |   | - | - | WR           |   |   |   |   |   |

| Default  | 0   | -  | -  | -  | 0xF         |    |   |   | - | - | 0x03         |   |   |   |   |   |

The DDC bit disables delay compensation applied by the Motion Filter, see section 13.1.

ABSSEL configures the number of measurements from the sensor's fine (A) coils between every measurement from its coarse (B) coils, when valid. This number will be denoted ABSCOUNT. Please see section 1.2 for more details. ABSCOUNT is calculated from Equation 1:

### Equation 1

$$ABSCOUNT = 2^{ABSSEL}$$

The default value of ABSSEL is 0xF, or 15 in decimal. In this case the value of ABSCOUNT given by Equation 1 is 32768. When operating with the nominal sample interval (see section 6.5) this means a coarse measurement takes place approximately every second.

SUBTYPE is a property of the sensor. Precision sensors that include both fine and coarse coils have a SUBTYPE value greater than 1. SUBTYPE is the number of fine COS/SIN periods per coarse COS/SIN period. Basic sensors only have one COS/SIN pair of sensor coils, and their SUBTYPE value is 0. Please refer to the Type B Sensor Reference Manual for more details SUBTYPE.

A precision sensor's SUBTYPE value is included in its full name. For example the 25mm B3 Precision Through-Hole Sensor has SUBTYPE=3 (the number after "B"). If in doubt, please refer to the sensor's datasheet. Position measurements reported by the CAM622 will always be wrong unless SUBTYE is configured correctly for the connected sensor.

## 6.5 INTERVAL Register

INTERVAL controls the interval between the start times of successive Sensing Engine measurements.

**Table 27 INTERVAL Register**

| INTERVAL | 15             | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|----------------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Field    | INTERVAL[15:0] |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Access   | WR             |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Default  | 0x012C         |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

INTERVAL is nominally in multiples of 0.1 $\mu$ s, so that the relationship between sample interval in  $\mu$ s and INTERVAL is given by Equation 2:

### Equation 2

$$\text{Sample Interval}/\mu\text{s} = \text{INTERVAL} \times 0.1\mu\text{s}$$

For example, INTERVAL is 0x012C by default which is 300 decimal, so Sample Interval is  $300 \times 0.1\mu\text{s} = 30\mu\text{s}$ . INTERVAL must be set to this default value for ABN encoder outputs to function correctly.

These figures are subject to a tolerance associated with the CAM622's on-chip oscillator. This tolerance is specified in Table 10 ("CAM622 Frequency tolerance across parts and Operating Temperature").

## 6.6 FLTLVLS Register

FLTLVLS includes the filter level controls MAXFILTLVL and MINFILTLVL, arranged as in Table 28. Please refer to section 13 for details on how these are used.

**Table 28 FLTLVLS Register**

| FLTLVLS | 15              | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|-----------------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Field   | MAXFILTLVL[7:0] |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Access  | WR              |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Default | 0xFF            |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

## 6.7 HYAD Register

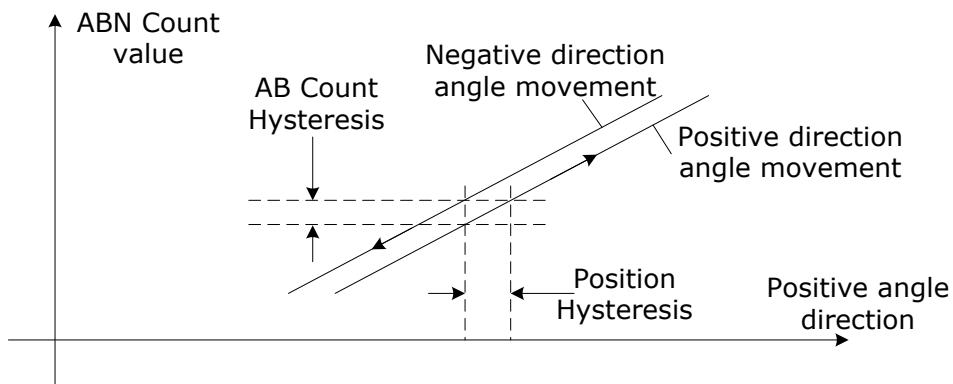

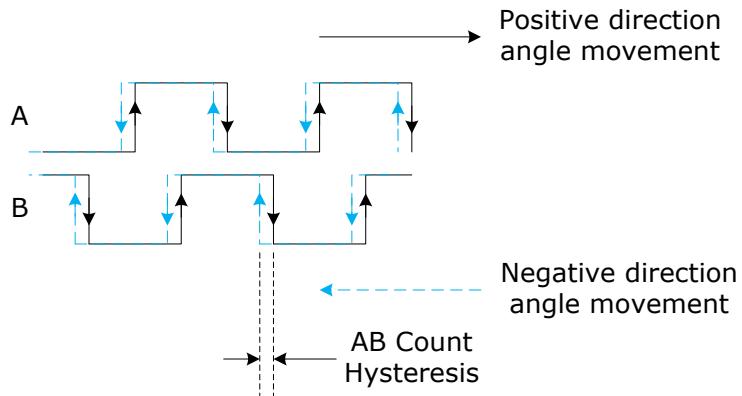

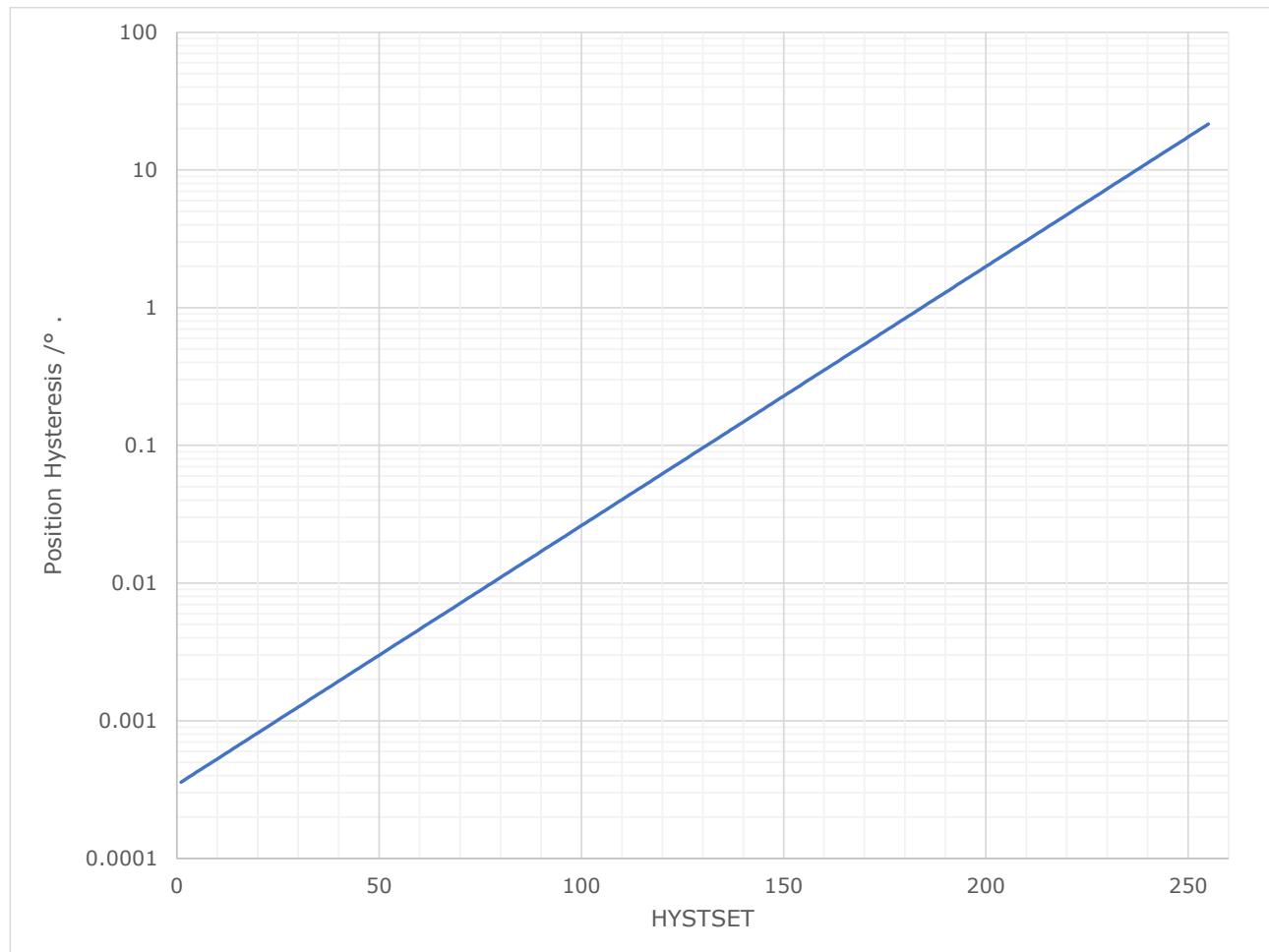

HYAD includes the HYSESET control which configures the amount of hysteresis added to position measurements when they are used to synthesise ABN encoder and UVW motor commutation signals. Please see section 9.7

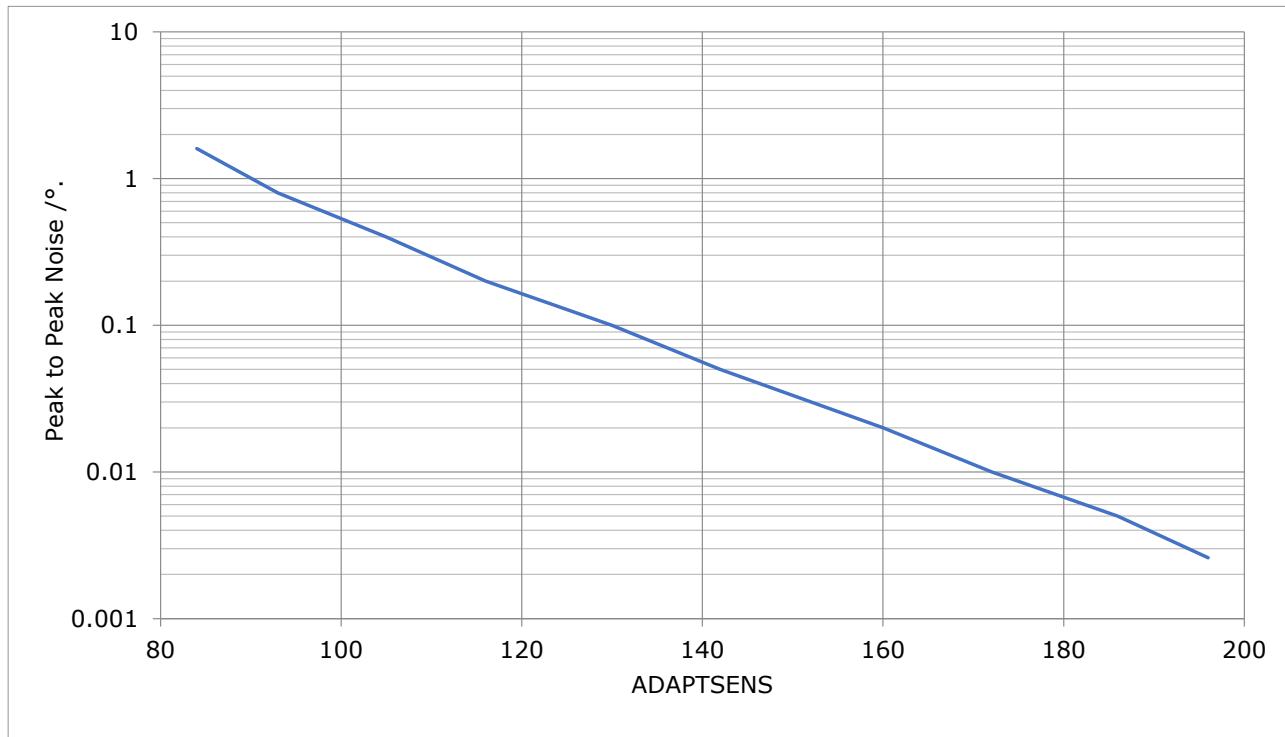

HYAD also includes ADAPTESENS, which controls the sensitivity of adaptive filtering. Please see section 13.5.

These registers are arranged as shown in Table 29.

**Table 29 HYAD Register**

| HYAD    | 15           | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|--------------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Field   | HYSTSET[7:0] |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Access  | WR           |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Default | 0x50         |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

## 6.8 SYS CONFIG Register

SYS CONFIG includes several fields and bits that control system operation, and its arrangement is shown in Table 30.

**Table 30 SYS CONFIG Register**

| SYS CONFIG    | 15         | 14   | 13      | 12   | 11    | 10      | 9       | 8  | 7  | 6  | 5            | 4  | 3 | 2 | 1 | 0 |

|---------------|------------|------|---------|------|-------|---------|---------|----|----|----|--------------|----|---|---|---|---|

| Field         | SYSID[3:0] | SAVE | FACTORY | BOOT | RESET | A1 CTRL | A0 CTRL | A1 | A0 | -  | EXTMODE[2:0] |    |   |   |   |   |

| Access (SPI)  | WR         | WR   | WR      | WR   | WR    | WR      | WR      | WR | WR | WR | -            | WR |   |   |   |   |

| Access (BiSS) | WR         | WR   | WR      | WR   | WR    | R       | R       | R  | R  | -  | WR           |    |   |   |   |   |

| Default       | 0xA        | 0    | 0       | 0    | 0     | -       | -       | 1  | 1  | -  | 2            |    |   |   |   |   |

SYSID is the System ID, whose value is read out of the CAM622 in the first word of each SPI transaction, see section 6.3. The host may change its value by writing a new value to SYS CONFIG.

The host uses the SAVE bit to signal to the CAM622 that register values should be written to non-volatile memory in preparation for standalone operation. It uses the FACTORY bit to return non-volatile memory to factory defaults. Please see section 8. When writing to SYS CONFIG for other reasons, the host must write 0 to SAVE and FACTORY.

Setting the BOOT bit puts the CAM622 into its bootloader mode in preparation for uploading new Application Code. Please refer to document "Uploading Application Code" for details of this process. When writing to SYS CONFIG for other reasons, the host must write 0 to BOOT.

When its RESET bit is set, the CAM622 performs a software reset following the SPI transaction. When writing to SYS CONFIG for other reasons, the host must write 0 to RESET.

The A0 and A1 bits control the states of the CAM622's A0 and A1 output pins. These are typically used to configure external devices. When set, A0CTRL and A1CTRL give control of A0 and A1 respectively to the CAM622, to support configurations including that of Figure 33 where the CAM622 controls A0 and/or A1 dynamically. The A0CTRL and A1CTRL bits can only be written over SPI, not BiSS. This is to prevent a host from changing settings over BiSS that might render BiSS unusable, potentially rendering the product unusable. The A0 setting can only be modified over BiSS if A0CTRL=0, and The A1 setting can only be modified over BiSS if A1CTRL=0. This is also to prevent a host from changing settings over BiSS that might render BiSS unusable.

EXTMODE controls the function of the EXT pin, as summarised in Table 31.

**Table 31 EXTMODE Function**

| EXTMODE[2:0] | Function                                          |

|--------------|---------------------------------------------------|

| 0            | Inactive (EXT = NOT EXTAH)                        |

| 1            | LED control                                       |

| 2            | Activates on VALID measurement                    |

| 3            | Reflects rotation direction when ABEN=1 and VALID |

| 4 – 7        | Reserved                                          |

When set to 1, EXT controls an LED, to provide a visible indication of status. EXT will activate when the CAM622 measurements are VALID with healthy signal level. It will toggle on and off repeatedly to indicate VALID measurements with low signal level. It will deactivate when measurements are not VALID. LEDTHRESHOLD configures the threshold between low and healthy signal level, and it is in units of reported amplitude (AMPA). Please refer to a sensor's datasheet for expected amplitude values. EXTAH controls whether EXT is active high (EXTAH=1) or active low (EXTAH=0), except when EXTMODE=3 when EXTAH is ignored. LEDTHRESHOLD and EXTAH are both fields in the SICONFIG register, see section 6.9 below.

## 6.9 SICONFIG Register

SICONFIG controls the behaviour of the CAM622's SI and EXT outputs. It includes the fields shown in Table 32.

**Table 32 SICONFIG register**

| SICONFIG | 15                    | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3     | 2    | 1    | 0 |

|----------|-----------------------|----|----|----|----|----|---|---|---|---|---|---|-------|------|------|---|

| Field    | LEDTHRESHOLD[11:0]    |    |    |    |    |    |   |   |   |   |   |   | EXTAH | SIAH | SIDO | - |

| Access   | WR                    |    |    |    |    |    |   |   |   |   |   |   | WR    | WR   | WR   | - |

| Default  | 0x0FA0 (decimal 4000) |    |    |    |    |    |   |   |   |   |   |   | 0     | 0    | 0    | - |

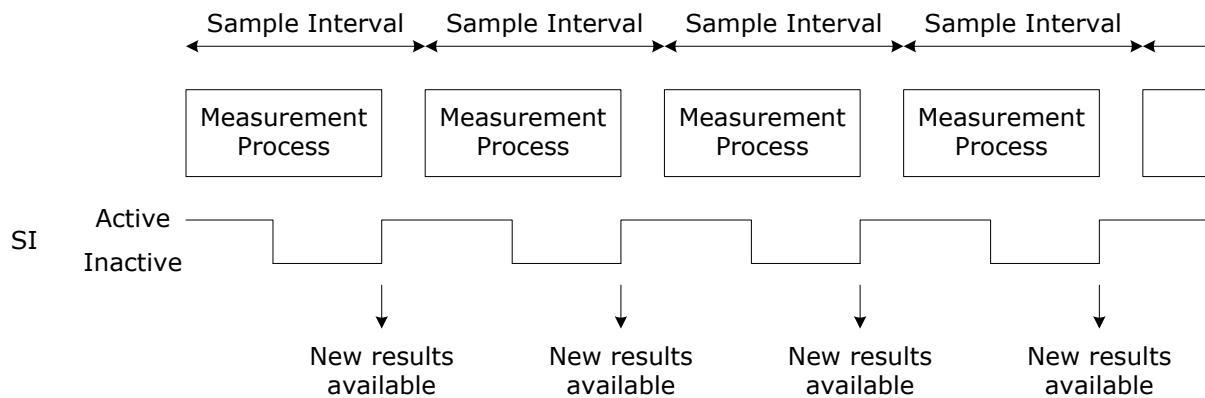

SI is a sample indicator output pin. It activates to indicate when each measurement completes, and new data is available from the Results Registers. A host may synchronise its SPI transactions to SI in order to minimise latency between actual position and obtaining measurements, see section 7.4. The SIAH bit configures whether SI is active high (SIAH=1) or active low (SIAH=0). The SIDO bit configures whether SI is a digital output (SIDO=1) or open drain (SIDO=0).

The functions of LEDTHRESHOLD and EXTAH are detailed in section 6.8 above.

## 6.10 INDEX10 and INDEX32 Registers

The 4 Information Registers (Table 14) are arranged immediately after the Results Registers. Their contents are configurable under host control, using the INDEX10 and INDEX32 registers. The Information Registers are arranged immediately after the Results Registers. An SPI host can read out Results Registers and Information Register values when the CAM622's ABN encoder outputs are enabled (ABEN=1). Indexing therefore allows a host to read selected register values faster than normal, and without the normal restriction preventing registers beyond address 0x10 from being accessed when ABEN=1.

**Table 33 INDEX10 Register**

| INDEX10 | 15 | 14          | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5           | 4 | 3 | 2 | 1 | 0 |

|---------|----|-------------|----|----|----|----|---|---|---|---|-------------|---|---|---|---|---|

| Field   | -  | INDEX1[6:0] |    |    |    |    |   |   |   | - | INDEX0[6:0] |   |   |   |   |   |

| Access  | -  | WR          |    |    |    |    |   |   |   | - | WR          |   |   |   |   |   |

| Default | 0  | 0x0D        |    |    |    |    |   |   |   | 0 | 0x0C        |   |   |   |   |   |

**Table 34 INDEX32 Register**

| INDEX32 | 15 | 14          | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5           | 4 | 3 | 2 | 1 | 0 |

|---------|----|-------------|----|----|----|----|---|---|---|---|-------------|---|---|---|---|---|

| Field   | -  | INDEX3[6:0] |    |    |    |    |   |   |   | - | INDEX2[6:0] |   |   |   |   |   |

| Access  | -  | WR          |    |    |    |    |   |   |   | - | WR          |   |   |   |   |   |

| Default | 0  | 0x0F        |    |    |    |    |   |   |   | 0 | 0x0E        |   |   |   |   |   |

The INDEX0 register controls the contents of INFO0 at address 0x0B. The INDEX1 register controls the contents of INFO1 at address 0x0C. The INDEX2 register controls the contents of INFO2 at address 0x0D. The INDEX3 register controls the contents of INFO3 at address 0x0E. In each case, the register value appearing in the respective INFO register is equal to the INDEX value plus 0x10.

The default value for INDEX0 shown in Table 33 makes INFO0 equal to  $0x0C + 0x10 = 0x1C$ , which is the address of the CAMID register. This therefore appears in INFO0 by default. Similarly INFO1 equals SYSVER, INFO2 equals BOOTVER and INFO3 equals SEVER by default.

## 6.11 ABCONFIG Register

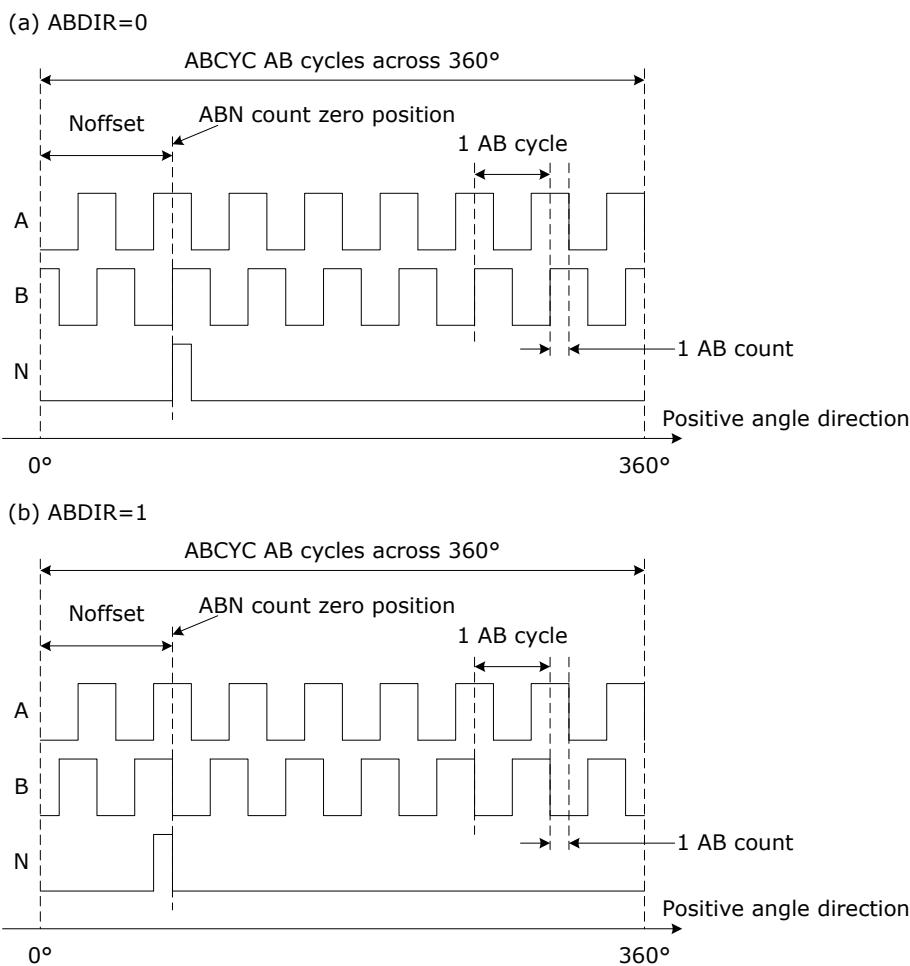

ABCONFIG configures the CAM622's encoder outputs LA, LB and LN, and includes the bits shown in Table 35.

**Table 35 ABCONFIG Register**

| <b>ABCONFIG</b> | <b>15</b> | <b>14</b> | <b>13</b> | <b>12</b> | <b>11</b> | <b>10</b> | <b>9</b> | <b>8</b> | <b>7</b> | <b>6</b> | <b>5</b> | <b>4</b> | <b>3</b> | <b>2</b> | <b>1</b> | <b>0</b> |

|-----------------|-----------|-----------|-----------|-----------|-----------|-----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Field           | ABEN      | -         | -         | -         | -         | -         | -        | -        | -        | -        | -        | NSTART   | ABDIR    | ANEG     | BNEG     | -        |

| Access          | WR        | -         | -         | -         | -         | -         | -        | -        | -        | -        | -        | WR       | WR       | WR       | WR       | -        |

| Default         | 0         | -         | -         | -         | -         | -         | -        | -        | -        | -        | -        | 1        | 0        | 0        | 0        | -        |

Please refer to section 9 for how to configure these bits, including their descriptions listed in Table 43.

Setting the ABEN bit enables the encoder outputs LA, LB and LN. When taking measurements over SPI, ABEN must be 0 for the CAM622 to respond to SPI transactions with a minimum of delay, and to allow Latch Point Compensation (section 13.6).

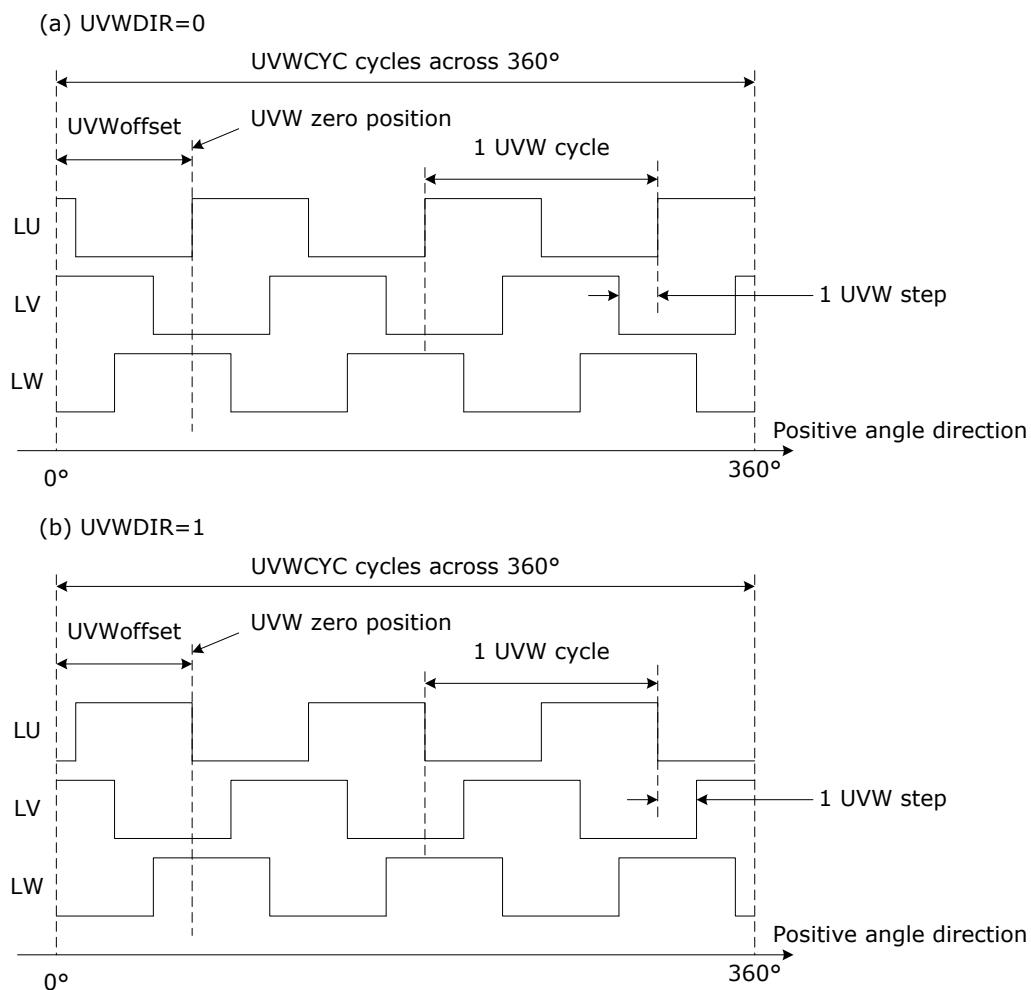

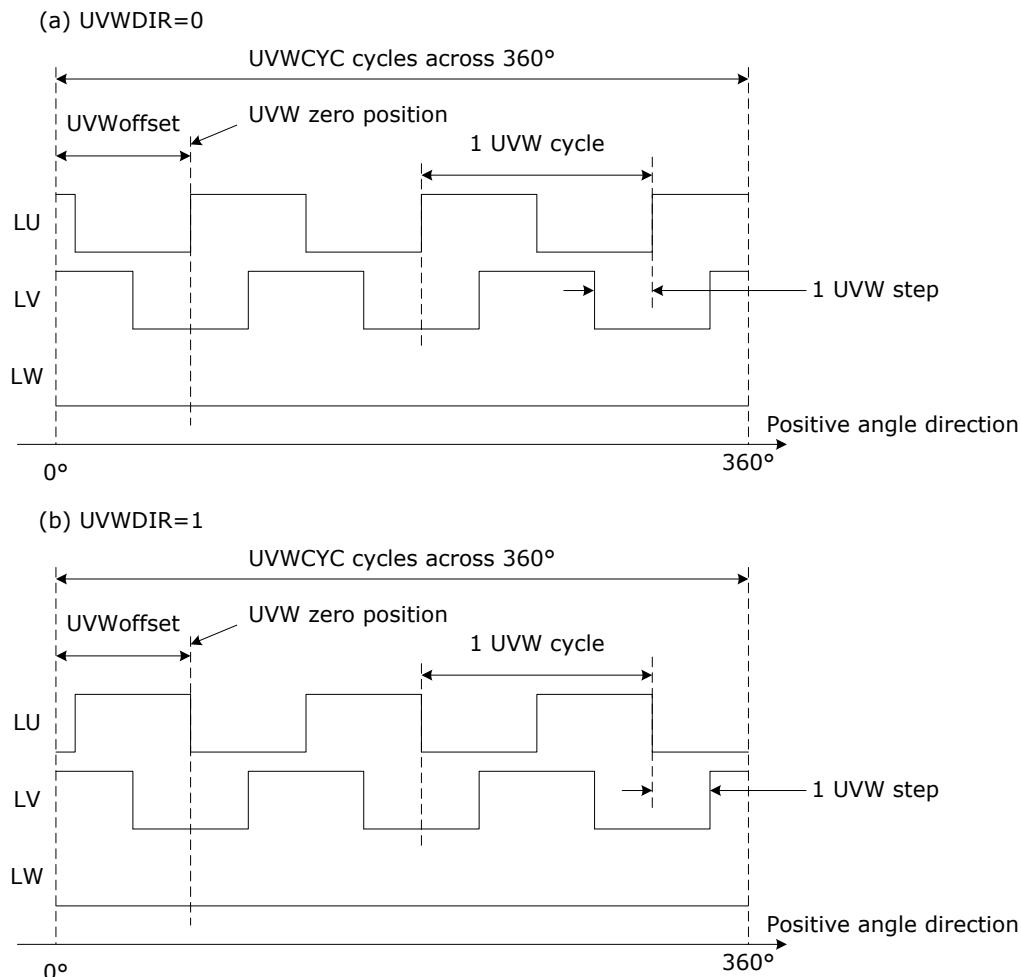

## 6.12 UVWCONFIG Register

UVWCONFIG configures the CAM622's motor commutation outputs U, V and W, and includes the bits shown in Table 36.

**Table 36 UVWCONFIG Register**

| <b>UVWCONFIG</b> | <b>15</b> | <b>14</b> | <b>13</b> | <b>12</b> | <b>11</b> | <b>10</b> | <b>9</b> | <b>8</b> | <b>7</b> | <b>6</b> | <b>5</b> | <b>4</b> | <b>3</b> | <b>2</b> | <b>1</b> | <b>0</b> |

|------------------|-----------|-----------|-----------|-----------|-----------|-----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Field            | UVWEN     | -         | -         | -         | -         | -         | -        | -        | -        | -        | -        | -        | UVWDIR   | -        | -        | 2PH      |

| Access           | WR        | -         | -         | -         | -         | -         | -        | -        | -        | -        | -        | -        | WR       | -        | -        | WR       |

| Default          | 0         | -         | -         | -         | -         | -         | -        | -        | -        | -        | -        | -        | 0        | -        | -        | 0        |

Please refer to section 12 for how to configure these bits.

Setting the UVWEN bit enables the motor commutation outputs U, V and W. When taking measurements over SPI, UVWEN must be 0 for the CAM622 to respond to SPI transactions with a minimum of delay, and to allow Latch Point Compensation (section 13.6).

## 6.13 BISSCONFIG Register

BISSCONFIG configures the CAM622 for communication over an optional BiSS interface.

**Table 37 BISSCONFIG Register**

| <b>BISSCONFIG</b> | <b>15</b> | <b>14</b> | <b>13</b> | <b>12</b> | <b>11</b> | <b>10</b> | <b>9</b> | <b>8</b> | <b>7</b> | <b>6</b> | <b>5</b> | <b>4</b> | <b>3</b> | <b>2</b> | <b>1</b>         | <b>0</b> |

|-------------------|-----------|-----------|-----------|-----------|-----------|-----------|----------|----------|----------|----------|----------|----------|----------|----------|------------------|----------|

| Field             | BISSEN    | ESE       | CB_SLO    | -         | -         | -         | -        | EDS      | -        | -        | -        | -        | -        | -        | BISS FORMAT[3:0] |          |

| Access (SPI)      | RW        | RW        | RW        | -         | -         | -         | -        | RW       | -        | -        | -        | -        | -        | -        | RW               |          |

| Access (BiSS)     | R         | R         | R         | -         | -         | -         | -        | RW       | -        | -        | -        | -        | -        | -        | RW               |          |

| Default           | 0         | 0         | 0         | 0         | 0         | 0         | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0x0              |          |

Please refer to Table 45 for how to configure these bits.

The BISSEN, ESE and CB\_SLO bits can only be written over SPI, not BiSS. This is to prevent a host from changing settings over BiSS that might render BiSS unusable, potentially rendering the product unusable.

## 6.14 BISSKEY Registers

The BISSKEY0 and BISSKEY1 registers are used to secure settings against unauthorised access over BiSS.

**Table 38 BISSKEY1 Register**

| <b>BISSKEY1</b> | <b>15</b>        | <b>14</b> | <b>13</b> | <b>12</b> | <b>11</b> | <b>10</b> | <b>9</b> | <b>8</b> | <b>7</b> | <b>6</b> | <b>5</b>       | <b>4</b> | <b>3</b> | <b>2</b> | <b>1</b> | <b>0</b> |

|-----------------|------------------|-----------|-----------|-----------|-----------|-----------|----------|----------|----------|----------|----------------|----------|----------|----------|----------|----------|

| Field           | BISSKEYCODE[7:0] |           |           |           |           |           |          |          |          |          | BISSKEY[23:16] |          |          |          |          |          |

| Access          | WR               |           |           |           |           |           |          |          |          |          | WR             |          |          |          |          |          |

| Default         | 0x00             |           |           |           |           |           |          |          |          |          | 0x00           |          |          |          |          |          |

BISSKEY is a 24-bit field formed by combining the BISSKEY[24:16] bits in the BISSKEY1 register with the BISSKEY[15:0] bits in the BISSKEY0 register.

Please refer to Table 45 for how to configure KEYCODE and BISSKEY.

## 6.15 SENTCONFIG Registers

The SENTCOFIG1 and SENTCOFIG2 registers are used to configure the CAM622's SENT interface, which is detailed in section 11. Please refer to Table 56 for the functions of these registers.

**Table 39 SENTCONFIG1**

| <b>SENTCONFIG1</b> | <b>15</b> | <b>14</b> | <b>13</b> | <b>12</b> | <b>11</b> | <b>10</b> | <b>9</b> | <b>8</b> | <b>7</b> | <b>6</b> | <b>5</b> | <b>4</b> | <b>3</b> | <b>2</b> | <b>1</b>         | <b>0</b> |

|--------------------|-----------|-----------|-----------|-----------|-----------|-----------|----------|----------|----------|----------|----------|----------|----------|----------|------------------|----------|

| Field              | SENT EN   | SENT POL  | SENT OD   | -         | -         | -         | -        | -        | -        | -        | -        | -        | -        | -        | SENT FORMAT[3:0] |          |

| Access             | RW        | RW        | RW        | -         | -         | -         | -        | -        | -        | -        | -        | -        | -        | -        | RW               |          |

| Default            | 0         | 0         | 0         | 0         | 0         | 0         | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0x0              |          |

**Table 40 SENTCONFIG2**

| <b>SENTCONFIG2</b> | <b>15</b>     | <b>14</b> | <b>13</b> | <b>12</b> | <b>11</b> | <b>10</b> | <b>9</b> | <b>8</b> | <b>7</b> | <b>6</b> | <b>5</b>       | <b>4</b> | <b>3</b> | <b>2</b> | <b>1</b> | <b>0</b> |

|--------------------|---------------|-----------|-----------|-----------|-----------|-----------|----------|----------|----------|----------|----------------|----------|----------|----------|----------|----------|

| Field              | SENTTICK[7:0] |           |           |           |           |           |          |          |          |          | SENTCOUNT[7:0] |          |          |          |          |          |

| Access             | RW            |           |           |           |           |           |          |          |          |          | RW             |          |          |          |          |          |

| Default            | 0x1E          |           |           |           |           |           |          |          |          |          | 0x21           |          |          |          |          |          |

## 7 Reading Measurements Over SPI

This section explains how to connect a host to the CAM622 when SPI will be the primary means of communication. Please refer to section 8 for using SPI to configure the CAM622 for standalone operation.

### 7.1 Host Connections to CAM622 Circuitry

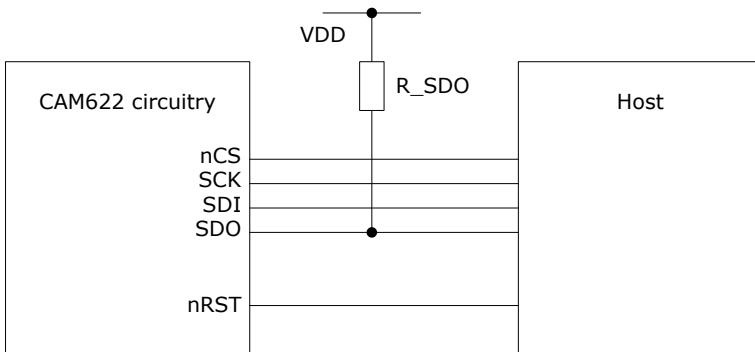

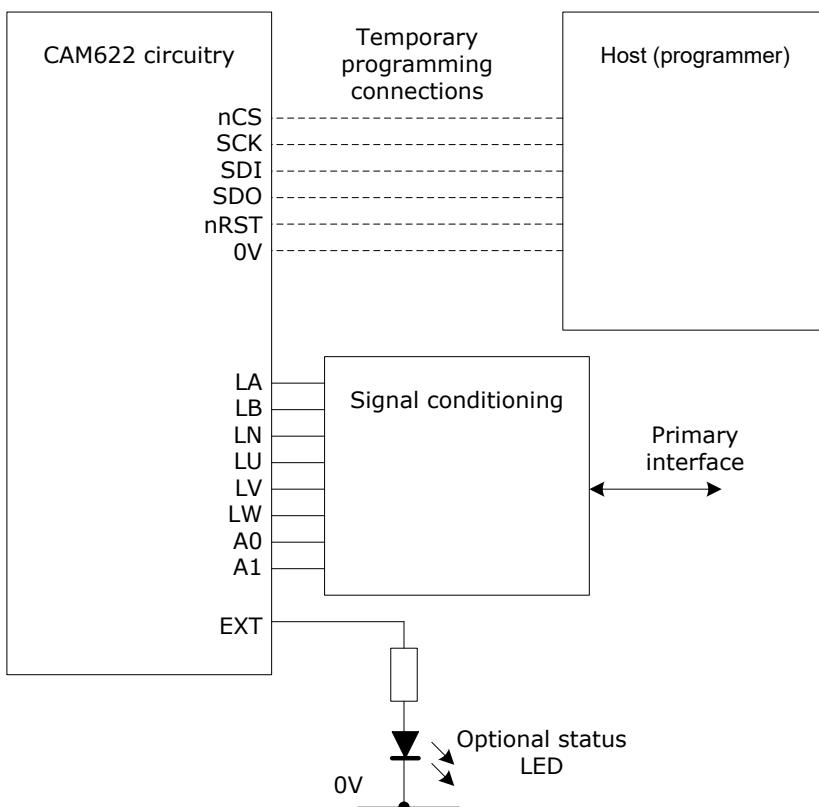

A host connects to the CAM622 circuitry of Figure 6 using the 4 SPI lines nCS, SCK, SDI and SDO, as illustrated in Figure 17. Host control over nRST is also strongly recommended, so that the host can put the CAM622 into a known state prior to operation.

An nRST connection also simplifies bootloader operation. Please refer to document "Updating Application Code" for details of how to program Application Code using the CAM622's bootloader.

**Figure 17 Host connections to CAM622 circuitry**

The CAM622 drives SDO high and low when nCS is low (SPI transaction in progress). When nCS is high, the CAM622 makes its SDO output a high impedance. This allows other devices to share the same SPI bus. To avoid SDO floating, a pull-up resistor is needed on SDO. If this can not be provided within the host device itself, it is recommended to add one: R\_SDO illustrated in Figure 17.

### 7.2 Factory Default Register Settings

This section assumes the CAM622 chip has not been configured for standalone operation. If it has, this is likely to interfere with taking measurements over SPI, because the CAM622 will contain non-default register values saved to non-volatile memory. For example, the ABEN bit is usually set for standalone operation, and this will interfere with SPI communication.

To avoid issues such as these, a CAM622 IC that was previously used for standalone operation should have its factory defaults restored, see section 8.5. Note that this operation should only be performed once or a small and limited number of times, to avoid exceeding the CAM622's specification for the maximum number of FLASH updates (Table 6). It must not be performed each time the CAM622 is used.

This is not normally an issue for production applications, because a CAM622 IC configured for standalone operation is unlikely to then be subsequently used inside a different product using SPI communication. It is more likely to be encountered during development, when care should be taken.

### 7.3 Measurement Process

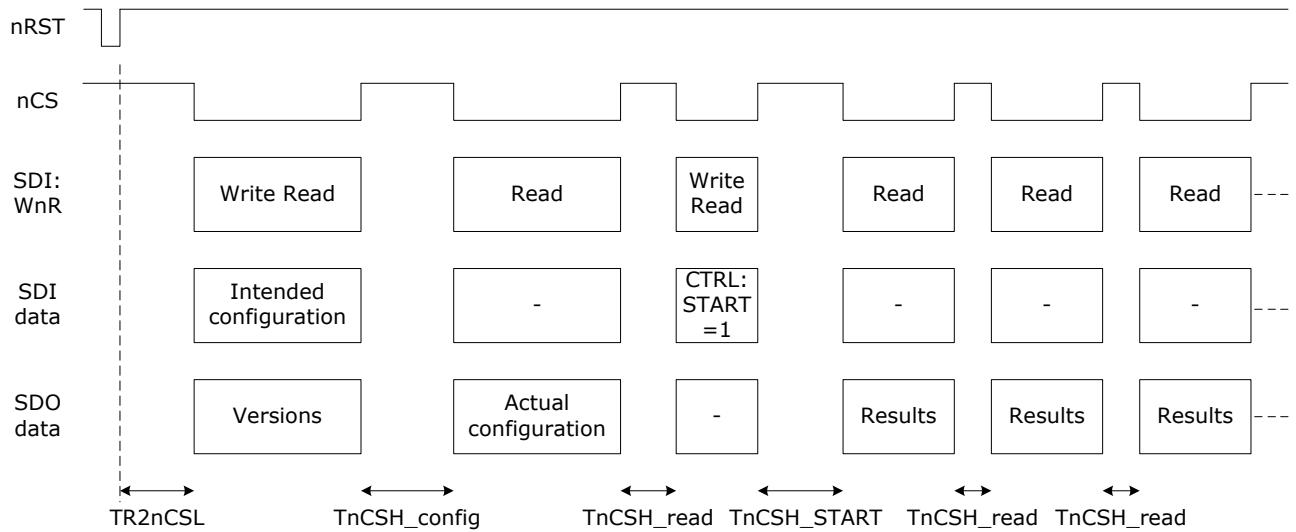

Figure 18 illustrates the process for communicating with the CAM622 over SPI, to configure it and then take repeated measurements.

**Figure 18 SPI transactions for taking repeated measurements**

The host starts the process by toggling nRST low to reset the CAM622. This puts the CAM622 into a known state, including default register values. A delay TR2nCSL(min) is then required before further SPI activity to allow the CAM622's internal self test and validity checking procedure to complete. TR2nCSL is described in section 5.3 and its minimum value is specified in Table 11.

The first SPI transaction is to write the intended register configuration to the CAM622, and read back its version numbers. This SPI transaction accesses all registers up to and including SYS CONFIG, or SICONFIG if Sample Indicators are used (section 7.4). Table 41 lists the registers to be accessed, and how to establish their values.

**Table 41 Registers requiring configuration for taking measurements over SPI**

| Register   | Field      | Value                                                                        | Section Ref |

|------------|------------|------------------------------------------------------------------------------|-------------|

| CTRL       | WnR        | 1: Write-read transaction.                                                   | 6.3         |

|            | START      | 0: Do not start measurements (this will be done in a later SPI transaction). |             |

| SECONFIG   | DDC        | Usually 0. Set to 1 to disable delay compensation.                           | 13.1        |

|            | ABSSEL     | Usually 15, for 32768 fine measurements between every coarse.                |             |

|            | SUBTYPE    | Set to match sensor's Subtype.                                               |             |