#### **Features**

- Pressure ranges: from 25mbar to 100mbar

- Pressure type:

- ✓ gage

- √ differential

- √ asymmetric differential

- 24 bits ADC

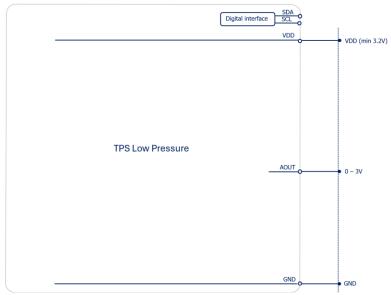

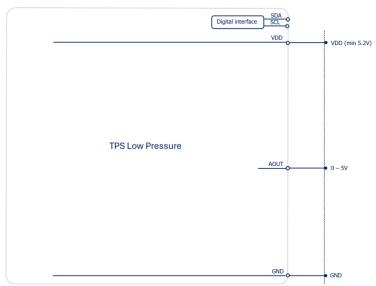

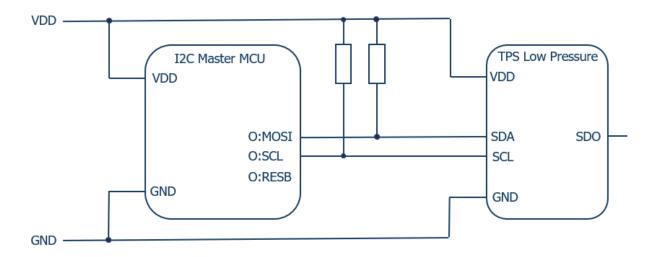

- I<sup>2</sup>C/ I<sup>3</sup>C digital and analog output interface available

- Pressure total error band : ± 1% FS (digital & analog)

- Pressure calibrated and temperature compensated output

- Compensated temperature range:

-20 to 85°C

#### **Applications**

- CPAP / Sleep Apnea

- Ventilators

- Gas Flow Instrumentation

- Air Flow Measurement

- HVAC / VAV

CLICK HERE > CONNECT WITH A SPECIALIST

# TPS LOW PRESSURE DIGITAL / ANALOG SENSOR

# **Gage & Differential Pressure Sensors**

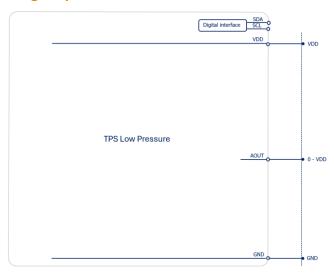

The TPS (TE Connectivity Pressure Sensors) are low pressure MEMS sensors offering state-of-the-art pressure transducer technology and CMOS mixed signal processing technology to produce either an analog and/or digital output fully conditioned, multi-order pressure and temperature compensated. This series provides JEDEC standard SOIC-16 package with dual vertical, dual horizontal or Manifold porting options. It is available in gage, differential and asymmetric differential configurations. With the dual porting, a reference measurement is possible to minimize errors due to changes in ambient pressure.

Combining the pressure sensor with a signal-conditioning ASIC in a single package simplifies the use of advanced silicon micro-machined pressure sensors. The pressure sensor can be mounted directly on a standard printed circuit board and a high level, calibrated pressure signal can be acquired from the digital interface. This eliminates the need for additional circuitry, such as a compensation network or microcontroller containing a custom correction algorithm.

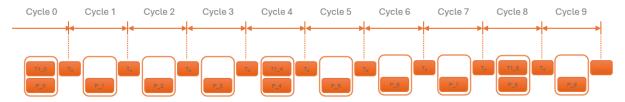

The TPS products are shipped in tape & reel.

# 1 PERFORMANCE SPECIFICATION

# 1.1 Available Part Number & Calibrated Pressure Ranges

Dual vertical port configuration :

| Part number | Part Description <sup>1</sup> | P <sub>MIN</sub> (mbar) | P <sub>MAX</sub> (mbar) |

|-------------|-------------------------------|-------------------------|-------------------------|

| 20030258-00 | TPS-070MG-CA1N-00-T           | 0                       | 70                      |

| 20032025-00 | TPS-070MG-CA2N-00-T           | 0                       | 70                      |

| 20032023-00 | TPS-025MG-CA1N-00-T           | 0                       | 25                      |

Dual horizontal port configuration :

| Part number | Part Description <sup>1</sup> | P <sub>MIN</sub> (mbar) | P <sub>MAX</sub> (mbar) |

|-------------|-------------------------------|-------------------------|-------------------------|

| 20032512-00 | TPS-040MD-BABN-00-T           | -40                     | 40                      |

#### Note:

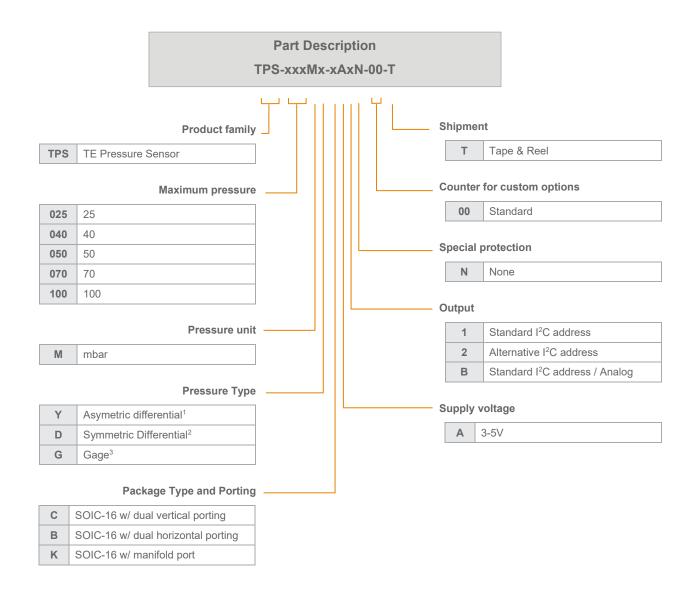

1. Part description is given on last datasheet page.

For specific part request, please contact TE representative for support.

# 1.2 Absolute Maximum Ratings

All parameters are specified at VDD = 5.0 V supply voltage at 25°C, unless otherwise noted.

| Characteristic                       | Symbol            | Min                                             | Max | Units |

|--------------------------------------|-------------------|-------------------------------------------------|-----|-------|

| Compensated Temperature              | T <sub>COMP</sub> | -20                                             | 85  | °C    |

| Operating Temperature <sup>(a)</sup> | Top               | -40                                             | 105 | °C    |

| Storage Temperature <sup>(a)</sup>   | T <sub>STG</sub>  | -40                                             | 125 | °C    |

| Supply Voltage                       | V <sub>DD</sub>   | -0.3                                            | 6   | V     |

| Media Compatibility <sup>(a)</sup>   |                   | Clean, dry air compatible with wetted materials |     |       |

#### Burst pressure and proof pressure by pressure range

| Part number                      | Proof Pressure <sup>(a, c)</sup><br>P <sub>Proof</sub> (mbar) | Burst Pressure <sup>(a,</sup> d) P <sub>Burst</sub> (mbar) |

|----------------------------------|---------------------------------------------------------------|------------------------------------------------------------|

| Up to P <sub>max</sub> = 40mbar  | 310                                                           | 415                                                        |

| Up to P <sub>max</sub> = 100mbar | 830                                                           | 1035                                                       |

#### Notes:

- a) Tested on a sample basis.

- b) Wetted materials include Silicon, glass, gold, aluminum, copper, silicone, epoxy, mold compound.

- c) Proof pressure is defined as the maximum pressure to which the device can be taken and still perform within specifications after returning to the operating pressure range.

- d) Burst pressure is the pressure at which the device suffers catastrophic failure resulting in pressure loss through the device.

# 1.3 ESD

| Description                    | Condition    | Symbol                | Min | Max | Units |

|--------------------------------|--------------|-----------------------|-----|-----|-------|

| ESD HBM Protection at all Pins | JEDEC JESD47 | V <sub>ESD(HBM)</sub> | -2  | 2   | kV    |

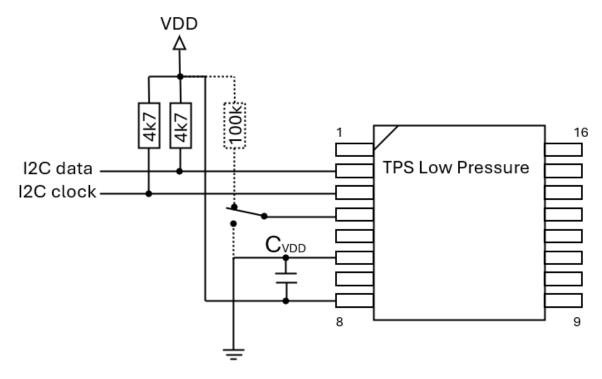

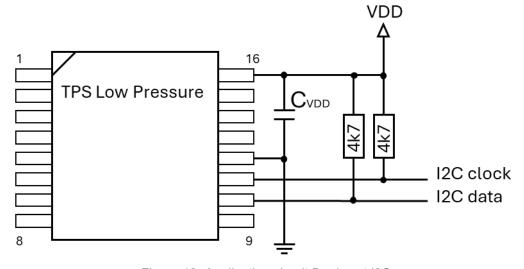

# 1.4 External Components

| Description             | Symbol    | Min | Тур | Max | Units |

|-------------------------|-----------|-----|-----|-----|-------|

| Supply bypass capacitor | $C_{VDD}$ |     | 100 |     | nF    |

# 1.5 Operating Conditions

| Parameter                                            | Symbol                        | Conditions                                                                                                                                 | Min | Тур                  | Max | Unit |

|------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------|-----|------|

| Supply Voltage                                       | VDD                           |                                                                                                                                            | 3.0 | 5.0                  | 5.5 | V    |

| Sleep supply Current                                 | Islp_25oC                     | VDD = 5.0V, T = 25°C<br>(no conversion, DAC off)                                                                                           |     | 1.8                  | 8   | μА   |

| Standby supply Current                               | Isty_25oC                     | VDD = 5.0V, T = 25°C<br>(no conversion, DAC off,<br>fast_start ="1")                                                                       |     | 156                  | 200 | μА   |

| Supply current during analog output                  | laout                         | VDD = 5.0 V, T = 25°C,<br>hvreg off, buffer on,<br>ratiometric output                                                                      |     | 362                  |     | μА   |

| Supply current during active conversion <sup>1</sup> | lac_p<br>lac_Tr<br>lac_Tdsvdd | VDD = 5.0 V, T = 25°C,<br>svdd = 1.8 V, fadc = 1 MHz<br>excluding sensor current<br>pressure<br>resistive temperature<br>diode temperature |     | 2058<br>1857<br>1715 |     | μА   |

| Parameter                                                                                                                                    | Symbol | Conditions                                                                                      | Min                                                                   | Тур                                                                   | Max                                                                   | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|------|

| Conversion time for 1 conversion (P or T1) based on: fadc = 1 MHz fast start no CRC with calculation with transfer add 10 us from sleep mode | Tconv  | OSR = 1<br>OSR = 2<br>OSR = 3<br>OSR = 4<br>OSR = 5<br>OSR = 6<br>OSR = 7<br>OSR = 8<br>OSR = 9 | 0.10<br>0.15<br>0.27<br>0.50<br>0.96<br>1.89<br>3.76<br>7.48<br>14.93 | 0.11<br>0.17<br>0.30<br>0.56<br>1.07<br>2.09<br>4.14<br>8.24<br>16.43 | 0.12<br>0.19<br>0.33<br>0.62<br>1.19<br>2.32<br>4.59<br>9.14<br>18.24 | ms   |

| Start up time                                                                                                                                | Tstart | Applying Power Supply to digital output ready                                                   |                                                                       | 16.2                                                                  |                                                                       | ms   |

| Wake up time                                                                                                                                 | Twaket | Wake up from sleep mode<br>Wake up from standby                                                 |                                                                       | 30<br>0                                                               |                                                                       | μS   |

| Digital I/O leakage                                                                                                                          | lleak  | VDD = 5.0 V, T = 25°C                                                                           | -1                                                                    |                                                                       | 1                                                                     | μΑ   |

#### Note:

- 1. Analog output add  $200\mu A$

- 2. Default osr is 4

# 1.6 Operating Characteristics Table

All parameters are specified at  $V_{DD}$  = 5.0 V supply voltage at 25°C, unless otherwise noted.

| Characteristic                                        | Symbol              | Min | Тур | Max | Units       |

|-------------------------------------------------------|---------------------|-----|-----|-----|-------------|

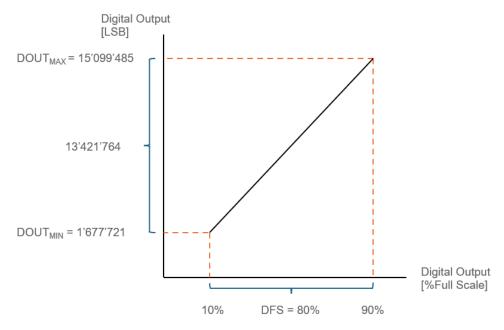

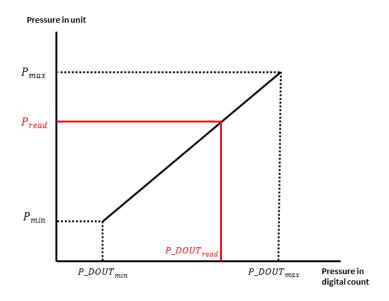

| Digital Pressure Output <sup>@</sup> P <sub>MIN</sub> | DOUT <sub>MIN</sub> |     | 10  |     | %Full Scale |

| Digital Pressure Output <sup>@</sup> P <sub>MAX</sub> | DOUT <sub>MAX</sub> |     | 90  |     | %Full Scale |

| Digital Full-Scale Span                               | DFS                 |     | 80  |     | %Full Scale |

| Resolution                                            |                     |     | 24  |     | Bits        |

| Digital Output Total Error Band                       | DACC                | -1  |     | +1  | %FS         |

| Analog Pressure Output <sup>@</sup> P <sub>MIN</sub>  | $AOUT_{MIN}$        |     | 10  |     | %VDD        |

| Analog Pressure Output <sup>@</sup> P <sub>MAX</sub>  | $AOUT_MAX$          |     | 90  |     | %VDD        |

| Analog Full-Scale Span                                | AFS                 |     | 80  |     | %VDD        |

| Analog Output Total Error Band                        | AACC                | -1  |     | +1  | %Full Scale |

| Temperature accuracy                                  | TACC                |     | 2   |     | °C          |

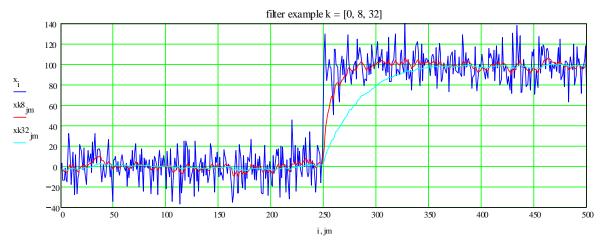

Figure 1: Digital Output / %FS Output

# 2 PACKAGE DIMENSIONS

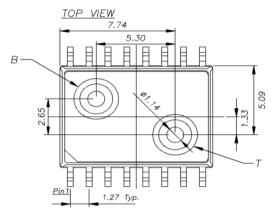

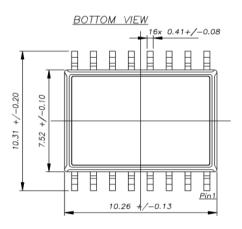

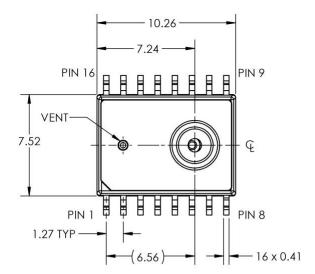

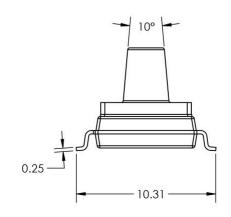

#### SOIC-16 Dual Vertical port (C) Package Dimensions

Lot number identification on top side

#### Notes:

- All dimensions in units of [mm]

- Moisture Sensitivity Level (MSL): Level 3

- · Wetted materials: Silicon, glass, gold, aluminum, copper, silicone, epoxy, mold compound.

- [B] is tube connected to bottom side of sensor die.

- [T] is tube connected to top side of sensor die. Topside pressure is positive pressure. An increase in topside pressure will result in an increase in sensor output.

- Bottom plate is anodized lid.

- Robust JEDEC SOIC-16 package for automated assembly

- Manufactured according to ISO9001, ISO14001 and ISO/TS 16949 standards

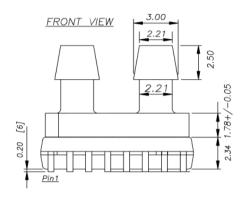

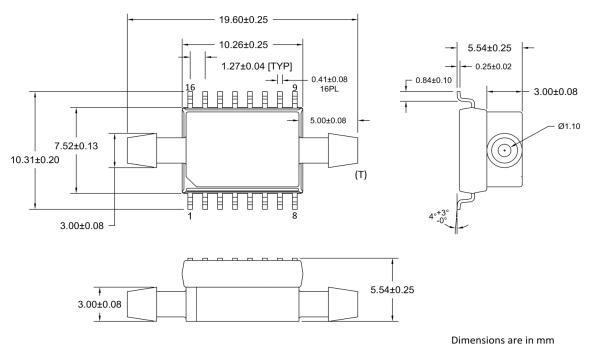

#### SOIC-16 Dual Horizontal port (B) Package Dimensions

Dimensions are in min

Lot number identification on top side

#### Notes:

- All dimensions in units of [mm]

- Moisture Sensitivity Level (MSL): Level 3

- Wetted materials: Silicon, glass, gold, aluminum, copper, silicone, epoxy, mold compound.

- [B] is tube connected to bottom side of sensor die.

- [T] is tube connected to top side of sensor die. Topside pressure is positive pressure. An increase in topside pressure will result in a increase in sensor output.

- Bottom plate is stainless steel

- Robust JEDEC SOIC-16 package for automated assembly

- Electrically isolate the bottom metal cover, do not connect to the cover and keep the board underneath free from electrical circuits.

- Manufactured according to ISO9001, ISO14001 and ISO/TS 16949 standards

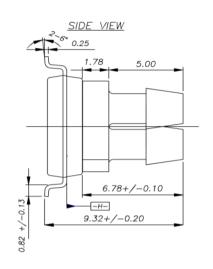

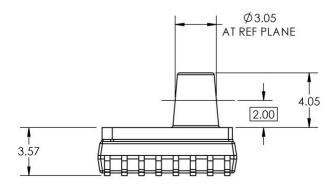

#### SOIC-16 Manifold port (K) Package Dimensions

Lot number identification on top side

#### Notes:

- All dimensions in units of [mm]

- Moisture Sensitivity Level (MSL): Level 3

- Wetted materials: Silicon, RTV, Epoxy, Plastic

- Pressure to the port is applied to the die back side

- Stainless steel lid

# 2.1 Pinout functions

### **Dual port**

|        | Dual port    |

|--------|--------------|

| Pin No | Pin Function |

| 1      | Aout         |

| 2      | -            |

| 3      | -            |

| 4      | -            |

| 5      | -            |

| 6      | -            |

| 7      | SDO          |

| 8      | -            |

| 9      | -            |

| 10     | SDA          |

| 11     | SCL          |

| 12     | VSS          |

| 13     | -            |

| 14     | -            |

| 15     | -            |

| 16     | VDD          |

#### Notes:

• SDO: Refer to chapter 7.

### **Manifold port**

|        | Manifold port |  |

|--------|---------------|--|

| Pin No | Pin Function  |  |

| 1      | -             |  |

| 2      | SDA           |  |

| 3      | SCL           |  |

| 4      | CSB           |  |

| 5      | -             |  |

| 6      | VSS           |  |

| 7      | _             |  |

| 8      | VDD           |  |

| 9      | _             |  |

| 10     | _             |  |

| 11     | -             |  |

| 12     | _             |  |

| 13     | _             |  |

| 14     | Aout          |  |

| 15     | SDO           |  |

| 16     | -             |  |

### Notes:

CSB : Refer to chapter 8.4.SDO : Refer to chapter 7.

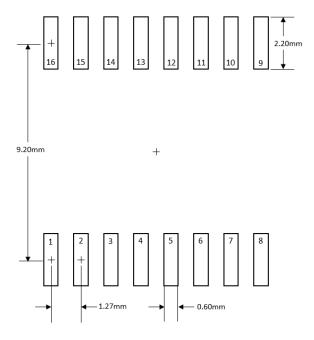

# 2.2 PCB design guidelines

Below suggested PCB footprint is recommended to ensure high mount assembly yields.

Following PCB finishes are compatible with SO16 package:

- Hot Air Solder Leveled (HASL)

- Organic Solderability Protectant (OSP)

- Electroless Nickel Immersion Gold (ENIG)

- Immersion Sn and Immersion Ag.

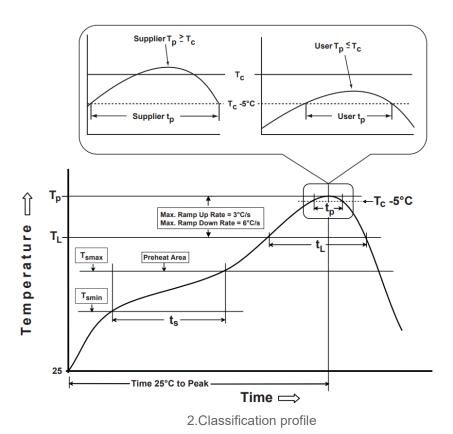

# 3 REFLOW PROFILE

The actual profile parameters depend upon the solder paste used. The recommendations from paste manufacturers should be followed.

Below recommendations may be used as alternative solution.

Table 5-2 Classification Reflow Profiles

| Profile Feature                                                                                                                                              | Sn-Pb Eutectic Assembly                                                                                                                                                 | Pb-Free Assembly                                                                                                                                                        |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Preheat/Soak Temperature Min (T <sub>smin</sub> ) Temperature Max (T <sub>smax</sub> ) Time (t <sub>s</sub> ) from (T <sub>smin</sub> to T <sub>smax</sub> ) | 100 °C<br>150 °C<br>60-120 seconds                                                                                                                                      | 150 °C<br>200 °C<br>60-120 seconds                                                                                                                                      |  |  |  |

| Ramp-up rate (T <sub>L</sub> to T <sub>p</sub> )                                                                                                             | 3 °C/second max.                                                                                                                                                        | 3 °C/second max.                                                                                                                                                        |  |  |  |

| Liquidous temperature (T <sub>L</sub> )<br>Time (t <sub>L</sub> ) maintained above T <sub>L</sub>                                                            | 183 °C<br>60-150 seconds                                                                                                                                                | 217 °C<br>60-150 seconds                                                                                                                                                |  |  |  |

| Peak package body temperature (T <sub>p</sub> )                                                                                                              | For users T <sub>p</sub> must not exceed the Classification temp in Table 4-1.  For suppliers T <sub>p</sub> must equal or exceed the Classification temp in Table 4-1. | For users T <sub>p</sub> must not exceed the Classification temp in Table 4-2.  For suppliers T <sub>p</sub> must equal or exceed the Classification temp in Table 4-2. |  |  |  |

| Time $(t_p)^*$ within 5 °C of the specified classification temperature $(T_c)$ , see Figure 5-1.                                                             | 20* seconds                                                                                                                                                             | 30* seconds                                                                                                                                                             |  |  |  |

| Ramp-down rate (T <sub>p</sub> to T <sub>L</sub> )                                                                                                           | 6 °C/second max.                                                                                                                                                        | 6 °C/second max.                                                                                                                                                        |  |  |  |

| Time 25 °C to peak temperature                                                                                                                               | 6 minutes max.                                                                                                                                                          | 8 minutes max.                                                                                                                                                          |  |  |  |

| * Tolerance for peak profile temperature $(T_n)$ is defined as a supplier minimum and a user maximum.                                                        |                                                                                                                                                                         |                                                                                                                                                                         |  |  |  |

1. Classification reflow profile

# 4 FUNCTIONAL BLOCK

# 4.1 Memory

The TPS Low Pressure sensor implements 2 major types of memory:

- 1. A few-time-programmable (FTP) non-volatile memory (NVM) of 32 words accessible in Read/Write.

- 2. Registers implemented as Flip-Flops.

At the start, the NVM will be copied into the register.

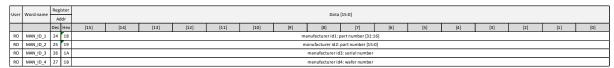

### 4.1.1 Non-Volatile Memory Mapping (NVM)

The TPS Low Pressure uses a memory IP that is a few-time-programmable (FTP) nonvolatile memory (NVM). This NVM is used to keep configuration data while not powered.

The user can access the NVM address 0 to 31 as shown in the Table 1: User memory

NVM can be directly accessed via the interface commands Erase/Write/Read NVM.

### 4.1.2 Register

Typically, registers are physically instantiated as Flip-Flops. Access to registers is direct via the interface commands *Write/Read* register.

The following convention is used:

- RO : Read in normal mode. Write in Unlock mode

- RW : Read/Write in normal mode

- RW\*: Read/Write special behavior

- · R: Read only

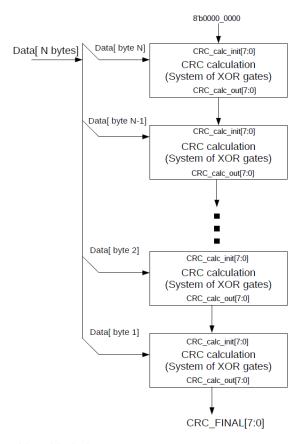

The memory's integrity is verified directly on the register through a CRC check. This verification can be independently activated for each page using the "en\_crc\_px" flag.

If a CRC error is detected, the "crc\_reg" flag in the "int\_0" register will toggle to "1". However, this error does not halt the conversion processes.

# 4.1.3 User Memory

| 71   [6]   [5]   [4]   [3]   [5]   [6]   [5]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   [6]   | . User | Word name    | Register | is. |                     |               |      |                 |                |        | Data [15:0]          | [6              |         |              |                 |                |         |           |                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------|----------|-----|---------------------|---------------|------|-----------------|----------------|--------|----------------------|-----------------|---------|--------------|-----------------|----------------|---------|-----------|-----------------|

| Pietrica   Sig   Sig   Pietrica   Pietrica |        |              | Addr     |     |                     |               |      |                 |                |        |                      |                 |         |              |                 |                |         |           |                 |

| Triple   5   5   5   1   1   1   1   1   1   1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |              | Dec      |     | [14]                | [13]          | [12] | [11]            | [10]           | [6]    | [8]                  | [7]             | [9]     | [2]          | [4]             | [3]            |         | [2]       | [2] [1]         |

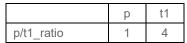

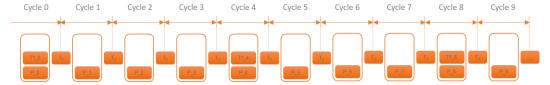

| Figure   5   6   6   A   A   A   A   A   A   A   A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RW     | PRES_4       | _        | 12  |                     |               |      |                 |                |        | p_ratio[2:0]         |                 |         | p_filt[2:0]  |                 |                |         | p_o       | p_osr[3:0]      |

| First Part                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RW     | TEMP1_4      | _        | .2  |                     |               |      |                 |                |        | t1_ratio[2:0]        |                 |         | t1_filt[2:0] |                 |                |         | t1_0      | t1_osr[3:0]     |

| Page 100   Ag   Ag   Ag   Ag   Ag   Ag   Ag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RW     | RESERVED     |          | 33  |                     |               |      |                 |                |        |                      |                 |         |              |                 |                |         |           |                 |

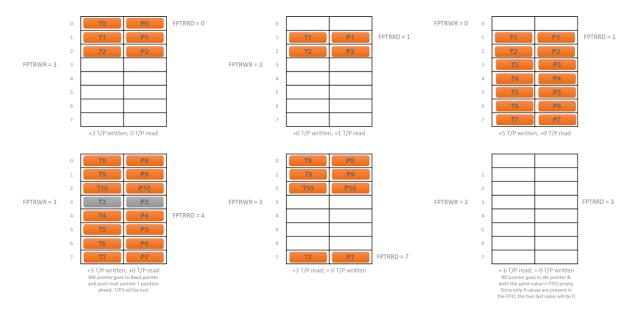

| DMC, 2                 DMC, 3                 Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                  Acc. clip_1Q20]                   Acc. clip_1Q20]                   Acc. clip_1Q20]                  Acc. clip_1Q20]                   Acc. clip_1Q20]                   Acc. clip_1Q20]                  Acc. clip_1Q20]                   Acc. clip_1Q20]                   Acc. clip_1Q20]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RW     | OPER         |          |     | fast_start          | int_cont_mode |      |                 |                | fifo_: | interrupt_threshold[ | [4:0]           |         | fifo_m       | ode[1:0]        |                |         | dela      | delay[3:0]      |

| POST, GAMP   202   64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | W.W.   | DAC_2        |          |     | dac_offset_comp_off | en_diag_ana   |      | dac_clip_h[2:0] |                |        | dac_clip_[[2:0]      |                 | dac_t   | drv_vdd      | _sel[1:0]       | dac_buff_mode  |         |           | dac_mode[2:0]   |

| Post Galvi 1   10   6   2   2   2   2   2   2   2   2   2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        | POST_GAIN_P  |          | 9.  |                     |               |      |                 |                |        | pgpp[15:C            | 0]              |         |              |                 |                |         |           |                 |

| KESNEND    20   60   50   50   50   50   50   50   5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | POST_GAIN_T1 | 103      | 4.  |                     |               |      |                 |                |        | t1gpp[15:0           | [0              |         |              |                 |                |         |           |                 |

| Fore Originary   12   6   4   1   1   1   1   1   1   1   1   1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | W.     | RESERVED     | _        | 89  |                     |               |      |                 |                |        |                      |                 |         |              |                 |                |         |           |                 |

| Fore Coff 1   10   6   2   2   2   2   2   2   2   2   2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W.W    | Post_OFF_P   |          | 6.  |                     |               |      |                 |                |        | popp[15:C            | 0]              |         |              |                 |                |         |           |                 |

| Figure   107   68   C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RW     | Post_OFF_T1  |          | r.  |                     |               |      |                 |                |        | t10pp[15:0           | 0]              |         |              |                 |                |         |           |                 |

| Total   Tota | W.     | RESERVED     | _        | 89  |                     |               |      |                 |                |        |                      |                 |         |              |                 |                |         |           |                 |

| LIMMT_1   110   61   111   110   61   111   110   61   111   110   61   111   61   111   61   111   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   61   | RW     | COM          |          | J.  |                     |               |      |                 |                |        | i2c_daisy_on         | en_spike_filter |         |              |                 | 12C programmat | ble add | ress[6:1] | ress[6:1]       |

| LIMMT_3   110   6F   11   11   6F   11   11   6F   11   11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RW     | LIMIT_1      | 109 6    | 0.  |                     |               |      |                 |                |        | p_thresh[15.         | [00:            |         |              |                 |                |         |           |                 |

| LIMMT_3   112   72   113   73   114   74   114   114   114   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115   115 | RW     | LIMIT_2      |          | Ę.  |                     |               |      |                 |                |        | p_thresl[15:         | [00:            |         |              |                 |                |         |           |                 |

| LIMMT_4   112   73   24   24   24   24   24   24   24   2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | W.W.   | LIMIT_3      | _        | H.  |                     |               |      |                 |                |        | t1_thres h[15        | 5:00]           |         |              |                 |                |         |           |                 |

| RESENTED         113         73         Amenal Lint, en         en_Ladc_error         e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RW     | LIMIT_4      |          | 0.  |                     |               |      |                 |                |        | t1_thresl[15         | [00:5           |         |              |                 |                |         |           |                 |

| NIT_EN_10         115         73         Seneral_Int_en         en_fdc_ency         en_adc_ency         en_adc_ency         en_adc_ency         en_fillip         en_fillip <t< th=""><th>RW</th><td>RESERVED</td><td></td><td>1.</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RW     | RESERVED     |          | 1.  |                     |               |      |                 |                |        |                      |                 |         |              |                 |                |         |           |                 |

| NT_EN_O                 15                 34                 Seneral_Int_en                 enaddcenral                 enaddcenral                enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 enaddcenral                 en                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | W      | RESERVED     |          | .2  |                     |               |      |                 |                |        |                      |                 |         |              |                 |                |         |           |                 |

| INT_EN_1         116         74         en3edcoufl1         en3edcoufl2         en3edcoufl2         en3edcoufl2         en3edcoufl2         en3edcoufl2         en3edcoufl2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | WW     | INT_EN_0     | 115 7    | 13  | general_int_en      | en_crc_com    |      |                 | en_adc_error   |        | en_sensor_error      | en_phigh        | en_plow | en_thigh     | en_tlow         | en_ffull       | en_f    | empty     | empty en_fthr   |

| NF_EN_2         11         75         en_senso_chk(15.0)           RESERVED_1         118         76         space for customer data           RESERVED_2         110         77         space for customer data           RESERVED_3         120         78         space for customer data           RESERVED_4         121         79         space for customer data           RESERVED_5         120         74         space for customer data           RESERVED_5         120         74         space for customer data           RESERVED_5         120         74         space for customer data           RESERVED_5         120         75         space for customer data           RESERVED_6         120         75         space for customer data           RESERVED_7         120         75         space for customer data           RESERVED_6         120         75         space for customer data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RW     | INT_EN_1     | 116 7    | 74  |                     |               |      |                 | en_adc_udfl_t1 |        |                      |                 |         |              | en_calc_udfl_t1 | en_calc_udfl_p |         |           | en_calc_ovfl_t1 |

| RESENUED_A         118         74         Space for customer data           RESENUED_A         120         73         Space for customer data           RESENUED_A         121         74         Space for customer data           RESENUED_A         121         78         Space for customer data           RESENUED_A         123         74         Space for customer data           RESENUED_A         124         75         Space for customer data           RESENUED_A         125         70         Space for customer data           RESENUED_A         126         Space for customer data         Propositioner data           RESENUED_A         127         Space for customer data         Propositioner data           RESENUED_A         126         Space for customer data         Propositioner data           RESENUED_A         127         Space for customer data         Propositioner data           RESENUED_A         127         Space for customer data         Propositioner data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RW     | INT_EN_2     |          | 22  |                     |               |      |                 |                |        | en_sensor_chk        | k[15:0]         |         |              |                 |                |         |           |                 |

| RESENVED_2         119         77         Space for customer data           RESENVED_3         120         78         Space for customer data           RESENVED_4         121         79         Space for customer data           RESENVED_5         123         74         Space for customer data           RESENVED_7         124         7         Space for customer data           RESENVED_8         125         70         Space for customer data           RESENVED_8         125         70         Space for customer data           RESENVED_8         126         7         Space for customer data           RESENVED_9         126         7         Space for customer data           RESENVED_9         127         7         Space for customer data           RESENVED_9         126         7         Space for customer data           RESENVED_9         127         7         Space for customer data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RW     | RESERVED_1   |          | 9.  |                     |               |      |                 |                |        | space for custon     | ner data        |         |              |                 |                |         |           |                 |

| RESENVED_3         120         78         Space for customer data           RESENVED_4         12.7         79         Space for customer data           RESENVED_5         12.7         74         Space for customer data           RESENVED_6         12.7         70         Space for customer data           RESENVED_8         12.7         71         Space for customer data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RW     | RESERVED_2   |          | 7   |                     |               |      |                 |                |        | space for custon     | ner data        |         |              |                 |                |         |           |                 |

| RESENUED_4         121         79         space for customer data           RESENUED_5         123         7A         space for customer data           RESENUED_6         123         7A         space for customer data           RESENUED_8         124         7A         space for customer data           RESENUED_8         125         7A         space for customer data           RESENUED_8         126         7A         space for customer data           RESENUED_8         126         7A         space for customer data           CRC_USER_MEM_127         7F         7F         space for customer data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RW     | RESERVED_3   |          | 8.  |                     |               |      |                 |                |        | space for custon     | ner data        |         |              |                 |                |         |           |                 |