# KTH7112 Series

16-bit High-Speed High-Precision

On-Axis Magnetic Encoder

Programmable Multi-Interface Angle Sensor

with ABZ/UVW/PWM/SPI/SSI Outputs

Technical Support sales.global@conntek.com.cn

#### Disclaimer

The information in this document is provided by Quanzhou KTsense Microelectronics Co., Ltd. (泉州昆泰芯微电子科技有限公司) (hereafter referred to as "KTsense Micro") on an "as is" basis for informational purposes only. KTsense Micro does not guarantee the accuracy of the information contained herein or the outcomes of its implementation. KTsense Micro assumes no liability for any errors or inaccuracies that may be present in this document. Users assume full responsibility for the application of the practices outlined in this document.

KTsense Micro owns the registered trademark CONNTEK, under which the CONNTEK brand sensors are marketed.

This document comes without any warranties, express or implied, including but not limited to warranties of merchantability, satisfactory quality, non-infringement, and fitness for a particular purpose. KTsense Micro, along with its employees, agents, and affiliates, is not liable for any losses arising from the use or reliance on this document.

This document is subject to change without prior notice and should not be construed as a commitment by KTsense Micro. Users should ensure they have the latest version of the relevant information before placing orders or integrating the product into their systems.

Users must evaluate the suitability of the product described in this document for their specific applications, including the required level of reliability and fitness for purpose.

This document and the described product may be subject to export control regulations. Export may require prior authorization from the competent authorities. The product is not intended, authorized, or warranted for use in applications requiring extended temperature ranges or unusual environmental conditions. High reliability applications, such as medical life-support or aviation systems, are specifically excluded.

The product may not be used for the development, production, maintenance, or storage of:

- 1. Chemical, biological, or nuclear weapons, including missile systems for such weapons.

- 2. Civil firearms, including spare parts or ammunition.

- 3. Defense-related products or materials for military or law enforcement use.

- 4. Applications that could cause serious harm to persons or property and that can be used as a means of violence in armed conflicts or similar situations.

No licenses or rights to any intellectual property of KTsense Micro or third parties are granted.

If this document is marked as "confidential" or similar, or if the content is reasonably understood to be confidential, the recipient must not disclose any part of the document to third parties without the express written consent of KTsense Micro. The recipient must take all necessary measures to maintain the confidentiality of the document, using at least the same degree of care as they use to protect their own confidential information, but no less than a reasonable degree of care. The recipient may only disclose the document to employees on a need-to-know basis, provided they are bound by confidentiality terms similar to those in this disclaimer. The document may only be used for the purpose for which it was received and may not be used for commercial purposes or to the detriment of KTsense Micro or its customers. These confidentiality obligations will last indefinitely but in any case, for no less than 10 years from the receipt of the document.

This disclaimer is governed by the laws of China, and any disputes arising from it will be subject to the exclusive jurisdiction of the courts in Shenzhen, China.

The invalidity of any provision in this disclaimer does not affect the validity of the remaining provisions. Previous versions of this document are repealed.

### Copyright

This document and its contents are protected by copyright law. No part of this document may be reproduced or distributed in any form or manner without the prior written consent of KTsense Micro.

#### **Contact Information**

For the latest version of this document, go to our website at https://en.conntek.com.cn/.

For additional information, please contact our Direct Sales team and get help for your specific needs:

| Region   | Contact Information                |

|----------|------------------------------------|

| Overseas | Email: sales.global@conntek.com.cn |

| China    | Email: sales@conntek.com.cn        |

### **Table of Contents**

| 1  | Product Information                                                                                                                                                                                               | 6                          |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|    | 1.1 Features1.2 Typical Applications1.3 General Description                                                                                                                                                       | 6                          |

| 2  | System Overview                                                                                                                                                                                                   | 7                          |

| _  | <ul> <li>2.1 System Architecture</li> <li>2.2 Recommended Application Circuit</li> <li>2.3 Pin Definition</li> <li>2.4 Interface Output Selection</li> <li>2.5 16-bit Binary Angle Encoding</li> </ul>            | 7<br>8<br>9<br>10          |

| 3  | Key Parameters                                                                                                                                                                                                    | 10                         |

|    | Magnet Installation Guide          4.1 On-Axis Magnet Installation          Register Configuration                                                                                                                | 11                         |

|    | <b>5.1</b> Register Map <b>5.2</b> Register Description                                                                                                                                                           |                            |

| 6  | <ul> <li>SPI Interface.</li> <li>6.1 SPI Timing</li> <li>6.2 Reading Absolute Angle via SPI</li> <li>6.3 Register Access Control</li> <li>6.4 Reading Registers.</li> <li>6.5 Writing Registers to MTP</li> </ul> | 13<br>13<br>14<br>14<br>15 |

| 7  | SSI Interface7.1 Timing Diagram7.2 Timing Parameters7.3 Data Frame Format                                                                                                                                         | 16<br>16                   |

| 8  | ABZ Interface  8.1 ABZ Output Resolution  8.2 ABZ Output Frequency Limiting  8.3 ABZ Startup Mode  8.4 ABZ Startup Delay                                                                                          | 17<br>18<br>18             |

| 9  | UVW Output.9.1 UVW Startup Delay.9.2 UVW and Z Signal Phase Relationship.                                                                                                                                         | 20                         |

| 10 | PWM Absolute Output  10.1 PWM Frequency Setting                                                                                                                                                                   | 21<br>21<br>22             |

| • • | Automatic Nonlinearity Calibration                                                                         | 22                          |

|-----|------------------------------------------------------------------------------------------------------------|-----------------------------|

|     | <b>11.1</b> Calibration Principle                                                                          |                             |

|     | <b>11.2</b> Calibration Status                                                                             | 22                          |

|     | <b>11.3</b> Calibration Methods                                                                            | 22                          |

|     | <b>11.4</b> Calibration Guidelines                                                                         | 23                          |

| 12  | System Operation Settings                                                                                  | 23                          |

|     | <b>12.1</b> Rotation Direction                                                                             | 23                          |

|     | <b>12.2</b> Zero Position Setting                                                                          |                             |

|     | <b>12.2.1</b> Automatic Zero Setting                                                                       | 24                          |

|     | <b>12.2.2</b> Manual Zero Position Setting                                                                 | 24                          |

|     | <b>12.3</b> Hysteresis                                                                                     |                             |

|     | <b>12.4</b> Digital Filter                                                                                 |                             |

| 13  | Product Selection Guide                                                                                    | 26                          |

| 14  | Ordering Information                                                                                       | 27                          |

| 15  | QFN-16L Package Information                                                                                | 27                          |

|     | <b>15.1</b> Package Drawing                                                                                | 27                          |

|     | 13.1 Fackage Diawing                                                                                       | 21                          |

|     | <b>15.2</b> Mechanical Dimensions                                                                          |                             |

| 16  | <b>15.2</b> Mechanical Dimensions                                                                          | 27                          |

| 16  | 15.2 Mechanical Dimensions                                                                                 | 27<br><b>28</b>             |

| 16  | <b>15.2</b> Mechanical Dimensions                                                                          | 27<br><b>28</b><br>28       |

|     | 15.2 Mechanical Dimensions                                                                                 | 27<br><b>28</b><br>28<br>28 |

|     | 15.2 Mechanical Dimensions  QFN-16L Tape and Reel Information  16.1 Package Drawing.  16.2 Tape Dimensions | 27<br>28<br>28<br>28<br>28  |

### 1 Product Information

#### 1.1 Features

The KTH7112 is a high-performance magnetic encoder with the following key features:

- 16-bit high-resolution absolute angle output

- On-axis application supported, with post-calibration INL error less than  $\pm 0.1^{\circ}$

- Supports both single-pole and multi-pole magnetic sources

- Ultra-low latency with a data update rate of  $1 \mu s$

- SPI communication interface with data rates up to 10 Mbps

- SSI interface supporting up to 5 Mbps for angle output

- $\bullet \;\;$  Programmable ABZ incremental output with 4 to 16384 steps per revolution

- Programmable UVW output for 1 to 32 pole pairs

- 12-bit PWM angle output, frequency adjustable, supports calibration status indication

- Built-in MTP (Multi-Time Programmable) memory for parameter storage

- Operating voltage: from 3.3 V to 5 V

- Operating temperature range: −40°C to 125°C

- Package: QFN3x3-16L

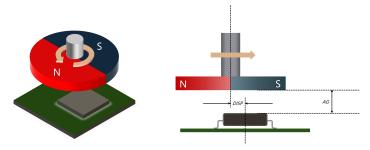

Figure 1: On-axis Configuration Example

### 1.2 Typical Applications

- Absolute angular position detection

- Brushless DC motor control

- Closed-loop stepper motor control systems

- Platform automatic door systems in rail transportation

### 1.3 General Description

The KTH7112 is a high-speed, high-precision magnetic encoder equipped with an advanced automatic nonlinearity calibration (ANLC) engine.

Users can initiate the calibration either by register configuration or via external pin trigger. The internal controller automatically measures nonlinear errors and calculates the compensation parameters. The calibration results are stored in internal MTP (Multi-Time Programmable) memory.

This calibration mechanism requires no external computation and can significantly enhance the linearity of angle measurement, achieving absolute accuracy better than  $\pm 0.1^{\circ}$ .

The encoder supports multiple interface modes to suit various applications:

- SPI Interface: A 3-wire SPI bus (CPOL=1, CPHA=1) is provided for reading 16-bit angle data, accessing internal registers, and configuring parameters. Data transmission includes an 8-bit CRC for error checking. This SPI interface does not support multiple CS lines; instead, multiple SDA lines can be connected to a microcontroller for data access.

- ABZ Incremental Output: Programmable ABZ quadrature signal output with resolutions up to 16384 steps/rev. It supports absolute position initialization upon power-up by emitting a sequence of AB pulses.

- **SSI Interface:** Supports two-wire synchronous serial communication with up to 5 Mbps data rate for absolute angle output.

- **PWM Output:** Offers a PWM signal with adjustable frequency (120 Hz to 3.8 kHz), and uses pulse width modulation to indicate angle or calibration status.

- **UVW Commutation Signal:** Programmable commutation outputs for 1 to 32 pole-pair configurations, ideal for BLDC applications.

These interface modes provide flexible and robust integration options for a wide range of system designs.

### 2 System Overview

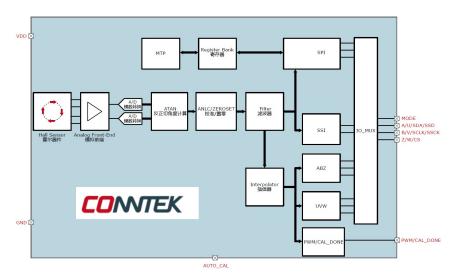

### 2.1 System Architecture

The KTH7112 integrates Hall sensors, analog front-end, analog-to-digital converters, and a digital signal chain to perform angle measurement and output digital signals.

The Hall sensors detect magnetic fields and generate analog voltages. These are converted into two orthogonal digital signals via ADCs. The

angle is calculated using an arctangent (ATAN) module, producing a 16-bit angle value. The angle is then processed through zero offset, rotation direction setting, and filtering.

Filtered angle data can be output directly via SPI or SSI interfaces. Alternatively, the angle can be converted into PWM signals based on duty cycle.

To enhance refresh rate, the filtered angle passes through an interpolator and is then output to the ABZ encoder module, which converts angle into quadrature incremental signals.

All system parameters are stored in non-volatile multi-time programmable (MTP) memory. Parameters can be configured via the SPI interface.

Figure 2: Functional Block Diagram

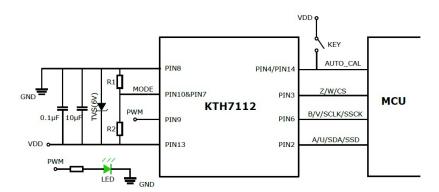

### 2.2 Recommended Application Circuit

Figure 3: Recommended Application Circuit

- R1 and R2 are  $5.1 \text{ k}\Omega$  pull-up resistors. Soldering R1 only enables 3-wire SPI. Soldering R2 only enables ABZ/UVW/SSI output.

- AUTO\_CAL pin can be externally triggered.

- PWM output can be connected to an LED to indicate calibration completion.

- PIN7 and PIN10 are both MODE pins and must be connected together with pull-up/pull-down resistors.

- PIN4 and PIN14 are both AUTO\_CAL pins. Either one can be used or neither needs to be connected.

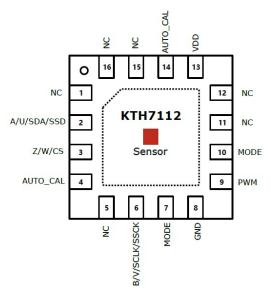

### 2.3 Pin Definition

Figure 4: QFN-16L Package Pinout

| Pin   | Name          | Function                                            |

|-------|---------------|-----------------------------------------------------|

| 1     | NC            | No connection, IO must be floating                  |

| 2     | A/U/SDA/SSD   | Function defined by MODE and IO_MUX                 |

| 3     | Z/W/CS        | Function defined by MODE and IO_MUX                 |

| 4     | AUTO_CAL      | External calibration trigger interface, active high |

| 5     | NC            | No connection, IO must be floating                  |

| 6     | B/V/SCLK/SSCK | Function defined by MODE and IO_MUX                 |

| 7     | MODE          | Interface output control                            |

| 8     | GND           | Ground                                              |

| 9     | PWM           | Duty cycle output                                   |

| 10    | MODE          | Interface output control                            |

| 11-12 | NC            | No connection, IO must be floating                  |

| 13    | VDD           | Power supply                                        |

| 14    | AUTO_CAL      | External calibration trigger interface, active high |

| 15–16 | NC            | No connection, IO must be floating                  |

| 17    | T-PAD         | Thermal pad, connect to GND                         |

Table 1: Pin Functions of KTH7112

### 2.4 Interface Output Selection

The interface output of KTH7112 is jointly controlled by PIN2 and the IO\_MUX register (detailed in Chapter 4, register address 0x10). It can output 3-wire SPI, ABZ, UVW, SSI, with specific specifications as follows:

| PIN and Register | State     | State      | State      | State      |

|------------------|-----------|------------|------------|------------|

| PIN10:MODE       | Low level | High level | High level | High level |

| IO_MUX[2:0]      | Any       | 0          | 1          | 2          |

| PIN2             | SDA       | A          | U          | SSD        |

| PIN6             | SCLK      | В          | V          | SSCK       |

| PIN3             | CS        | Z          | W          | Z          |

Table 2: Interface Output Selection

The output status of KTH7112's output interfaces PIN2, PIN6, PIN3 is jointly determined by the input status of PIN2 MODE and the IO\_MUX register. When MODE input is low, PIN2, PIN6, PIN3 are 3-wire SPI interfaces. When MODE input is high, if the IO\_MUX register is set to 0, it is ABZ output (default value); if the IO\_MUX register is set to 1, it is UVW output; if the IO\_MUX register is set to 2, it is SSD output.

### 2.5 16-bit Binary Angle Encoding

The angle is represented using a 16-bit binary value ranging from 0 to 65535, which corresponds to  $0^{\circ}$  to  $360^{\circ}$ .

$$\text{Angle (degrees)} = \frac{\text{Binary Value} \times 360}{2^{16}}$$

All angle outputs in this datasheet use this encoding format unless otherwise specified.

### 3 Key Parameters

| Parameter                | Min              | Тур                 | Max        |

|--------------------------|------------------|---------------------|------------|

| Supply Voltage           | 3.0 V            | 3.3 V               | 5.0 V      |

| Magnetic Field Strength  | $30~\mathrm{mT}$ | 60 mT               | 150 mT     |

| Operating Current        | _                | 16 mA               | _          |

| Start-up Time            | _                | 20 ms               | _          |

| Data Latency             | _                | $1~\mu$ s           | _          |

| Output Noise (1 sigma)   | _                | 0.015°              | _          |

| Integral Nonlinearity    | _                | ±0.1°               | _          |

| Maximum Rotational Speed | _                | _                   | 120000 rpm |

| ESD Protection (HBM)     | _                | $\pm 5~\mathrm{kV}$ | _          |

Table 3: Key Electrical and Performance Parameters @ 3.3 V Supply

## 4 Magnet Installation Guide

### 4.1 On-Axis Magnet Installation

| Parameter           | Description                                 | Min | Тур    | Max | Unit |

|---------------------|---------------------------------------------|-----|--------|-----|------|

| $D_{mag}$           | Diameter of radially magne-<br>tized magnet | _   | 10     | 30  | mm   |

| $T_{\sf mag}$       | Recommended magnet thick-<br>ness           | _   | 2.5    | 5   | mm   |

| $B_{pk}$            | Magnetic field at chip location             | 30  | _      | 150 | mT   |

| $A_{G}$             | Air gap                                     | _   | 1.0    | 5.0 | mm   |

| $R_{S}$             | Rotational speed                            | _   | _      | 120 | krpm |

| $\Delta_{\sf disp}$ | Installation offset tolerance               | _   | 0      | 1.0 | mm   |

| $TC_{mag1}$         | NdFeB magnet temperature coefficient        | _   | -0.120 | _   | %/°C |

| $TC_{mag2}$         | SmCo magnet temperature coefficient         |     | -0.035 | _   | %/°C |

Table 4: On-Axis Magnet Installation Recommendations

Recommended magnetic materials: NdFeB or SmCo.

Figure 5: Recommended Chip Placement for On-Axis Magnet

# **5 Register Configuration**

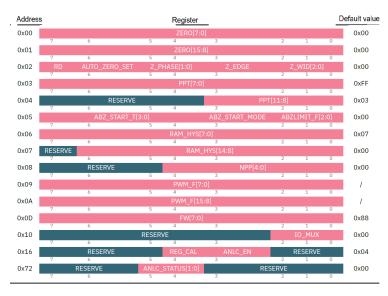

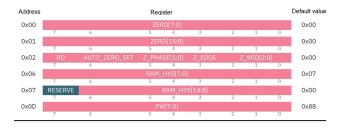

### 5.1 Register Map

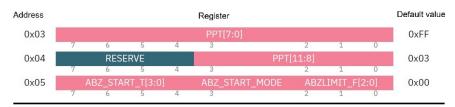

Figure 6: Detailed Register Bit Field Layout

### **5.2 Register Description**

| Symbol           | Default (dec) | Description                                         |

|------------------|---------------|-----------------------------------------------------|

| ZERO[15:0]       | 0             | Zero angle offset setting                           |

| RD               | 1             | Rotation direction: 1 for CW                        |

| AUTO_ZERO_SET    | 0             | Set to 1 to force output angle to zero              |

| Z_PHASE[1:0]     | 0             | Z signal phase for ABZ                              |

| Z_EDGE           | 0             | 0: rising edge of Z at zero angle, 1: falling edge  |

| Z_WID[2:0]       | 0             | Z signal width in LSBs                              |

| PPT[11:0]        | 1023          | ABZ resolution, default 1024 lines (4096 steps/rev) |

| ABZ_START_T[3:0] | 2             | ABZ output delay, default 20ms                      |

| ABZ_START_MODE   | 0             | 1: absolute ABZ startup mode                        |

| ABZLIMIT_F[2:0]  | 0             | ABZ max frequency limit, default 16MHz              |

| RAM_HYS[14:0]    | 7             | Hysteresis configuration for angle output           |

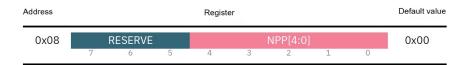

| NPP[4:0]         | 0             | UVW pole pair count, default 1                      |

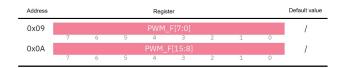

| PWM_F            | _             | PWM output frequency (factory calibrated to 1kHz)   |

| FW[7:0]          | 136           | Filter depth control                                |

| IO_MUX           | 0             | 0: ABZ, 1: UVW, 2: SSI output                       |

| REG_CAL          | 0             | Set to 1 to initiate self-calibration               |

| ANLC_EN          | 1             | Enable calibration effect on angle output           |

| ANLC_STATUS[1:0] | 0             | 0: Not started                                      |

| RESERVE          | 0             | Reserved, do not modify                             |

Table 5: Register Parameter Descriptions

### **6 SPI Interface**

KTH7112 employs a three-wire SPI communication protocol, operating in Mode 3 (CPOL = 1, CPHA = 1). This serial interface allows reading the absolute angle, accessing internal registers, and programming the MTP (Multiple-Time Programmable) memory. The maximum supported SPI communication speed is 10 Mbps.

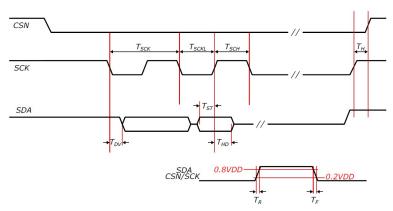

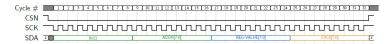

### 6.1 SPI Timing

The SPI timing diagram is shown in Figure 7. All timing parameters are measured under a load condition of  $20~\rm pF$ .

Figure 7: SPI Timing Diagram

Table 6: SPI Timing Parameters (20 pF Load)

| Symbol     | Description                                 | Min (ns) | Typ (ns) | Max (ns) |

|------------|---------------------------------------------|----------|----------|----------|

| $T_{SCK}$  | SCK clock period                            | 100      | _        | _        |

| $T_{SCKL}$ | SCK low-level period                        | 50       | _        | _        |

| $T_{SCKH}$ | SCK high-level period                       | 50       | _        | _        |

| $T_H$      | SCK rising edge to CSN rising edge interval | 120      | _        | _        |

| $T_R$      | Digital signal rise time                    | _        | 10       | _        |

| $T_F$      | Digital signal fall time                    | _        | 10       | _        |

| $T_{DV}$   | MISO data valid time                        | _        | _        | 50       |

| $T_{ST}$   | MOSI data setup time                        | 50       | _        | _        |

| $T_{HD}$   | MOSI data hold time                         | 50       | _        | _        |

These parameters are crucial for defining the SPI communication timing requirements. Adhering to these specifications in hardware and firmware design is essential to ensure reliable data transfer between the KTH7112 product's microcontroller and peripheral devices.

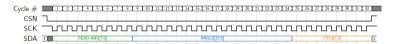

### 6.2 Reading Absolute Angle via SPI

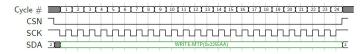

The steps for reading the angle are as follows:

- 1. Send command: 8-bit (0x00)

- 2. Receive data: 16-bit data + 8-bit CRC

- 3. The number of SCLKs sent for reading the angle can be adjusted according to your needs. For example, sending an 8-bit angle reading command, or only sending 8 SCLKs to read the high 8 bits of the angle, is also supported by the chip.

- 4. The interval between two SPI communications needs to be greater than 150 ns

- 5. CRC check adopts CRC-8/ITU standard:

- Polynomial:  $x^8 + x^2 + x + 1$  (0x07)

- Initial value: 0x00Result XOR value: 0x55

Figure 8: SPI Read Angle Sequence

### 6.3 Register Access Control

KTH7112 implements a locking mechanism for write access to its registers to ensure safe operation.

- Upon power-up, registers are locked and cannot be modified.

- Send 32-bit unlock key: 0x20240101

- Send 32-bit lock key: 0x20241231 to re-enable protection

- Register and angle read operations are always allowed

Figure 9: Unlocking Registers via SPI

Figure 10: Locking Registers via SPI

### 6.4 Reading Registers

The operation steps for reading registers:

- 1. Send command: 8-bit 0x11 + 8-bit register address

- 2. Receive data: 8-bit register value + 8-bit CRC

- 3. The high 16 bits are the read command input sent to the chip, and the low 16 bits are the returned register value and CRC check code

- 4. The interval between two SPI communications needs to be greater than  $150~\mathrm{ns}$

Figure 11: Register Read Operation via SPI

### 6.5 Writing Registers

The operation steps for writing registers:

- 1. First, you need to send the unlock code (32'h20240101)

- 2. Send command: 8-bit 0x33 + 8-bit register address + 8-bit write value

- 3. Receive data: 8-bit register value (New feature: returns the value written to the register in the same frame)

- 4. The 24th SCLK high-level duration must be greater than 100~ns

Important timing requirements:

- The interval between two SPI communications needs to be greater than 150 ns

- After the register write command, you must wait at least 100 ns before reading the return value

Figure 12: Register Write Operation via SPI

### 6.6 Writing Registers to MTP

All register writes are volatile unless explicitly saved to MTP (non-volatile memory). Use the following steps to burn MTP:

- 1. Ensure register access is unlocked

- 2. Send 24-bit MTP burn command: 0x2255AA

- 3. Wait at least 400 ms before any further SPI operation

#### Important precautions:

- MTP write is irreversible

- Validate all parameters before writing

- Do not power off during programming

- Use only verified and tested firmware for MTP operations

Figure 13: Writing Registers to MTP via SPI

### 7 SSI Interface

KTH7112 supports the SSI (Synchronous Serial Interface) protocol for absolute angle readout.

The device functions as an SSI slave and exclusively supports angle data transmission only. Register read or write operations are not supported via SSI. The transmitted data is MSB-first, meaning the most significant bit of the angle data is sent first.

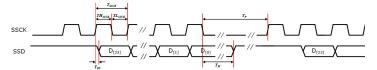

### 7.1 Timing Diagram

The standard SSI interface uses two signal lines:

- SSCK: Clock input from the master

- SSD: Serial data output from the sensor

The timing relationship between SSCK and SSD is shown in Figure 14.

Figure 14: SSI Timing Diagram

### 7.2 Timing Parameters

The electrical timing requirements for SSI communication are shown in Table 7. These values ensure proper synchronization between the host controller and the KTH7112 device.

| Symbol      | Description              | Min | Max | Unit    |

|-------------|--------------------------|-----|-----|---------|

| $t_{DV}$    | SSD data valid delay     | _   | 15  | ns      |

| $T_{SSCK}$  | SSCK clock period        | 0.2 | 10  | $\mu$ S |

| $T_{LSSCK}$ | SSCK low level duration  | 0.1 | 5   | $\mu$ S |

| $T_{HSSCK}$ | SSCK high level duration | 0.1 | 5   | $\mu$ S |

| $T_M$       | Monoflop timeout         | 10  | _   | $\mu$ S |

| $T_P$       | Inter-frame pause time   | 16  | _   | $\mu$ S |

Table 7: SSI Timing Parameters

#### 7.3 Data Frame Format

Each SSI data frame consists of:

- 16-bit absolute angle value

- 8-bit CRC code using the CRC-8/ITU standard

Data is shifted out synchronously on the falling edge of SSCK, with MSB transmitted first.

Figure 15: Standard SSI Angle Read Sequence

### 8 ABZ Interface

Figure 16: ABZ Output Related Register Settings

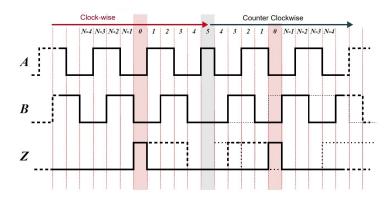

KTH7112 provides angular position output through the incremental ABZ interface. The interface is configured for 14-bit resolution, corresponding to 16384 steps per revolution, or 4096 pulse periods (PPT) per revolution on the AB signals.

The phase difference between signals A and B indicates the direction of rotation. In clockwise rotation, signal A leads and signal B follows. In counterclockwise rotation, signal B leads and signal A follows. During power-on, all three ABZ signals are held high.

When the magnet above the center of the chip (viewed from top) rotates counterclockwise (CCW), the rising edge of signal B leads that of signal A by 1/4 cycle. Conversely, during clockwise (CW) rotation, the rising edge of signal A leads that of signal B by 1/4 cycle. The phase relationship between A and B reverses as the rotation direction changes.

Figure 17: ABZ Output Timing Diagram

### 8.1 ABZ Output Resolution

The ABZ incremental interface of KTH7112 can support any integer resolution up to 4096 pulse periods per revolution. Users can program the internal MTP field <code>PPT[13:0]</code> to set a custom resolution. Common values are shown below:

Table 8: ABZ Resolution vs. PPT Settings

| PPT(11:0) | Pulse/Rev (PPT) | Steps/Rev |

|-----------|-----------------|-----------|

| 0         | 1               | 4         |

| 1         | 2               | 8         |

| 2         | 3               | 12        |

| ÷         | :               | :         |

| 4093      | 4094            | 16376     |

| 4094      | 4095            | 16380     |

| 4095      | 4096            | 16384     |

### 8.2 ABZ Output Frequency Limiting

The maximum AB edge output frequency is 16 MHz. This can be reduced by configuring the ABZLIMIT parameter, as shown below:

Table 9: ABZ Frequency Limit Settings

| ABZLIMIT | Max Edge Frequency |

|----------|--------------------|

| 0        | 16 MHz             |

| 1        | 8 MHz              |

| 2        | 4 MHz              |

| 3        | 2 MHz              |

| 4        | 1 MHz              |

### 8.3 ABZ Startup Mode

KTH7112 supports two ABZ startup modes, selectable via the  ${\tt ABZ\_START\_MODE}$  register:

- Normal startup (ABZ\_START\_MODE = 0): ABZ signals output incremental pulses immediately after power-on.

- Absolute startup (ABZ\_START\_MODE = 1): ABZ outputs a burst of pulses indicating the absolute position at startup.

In absolute startup mode, one clock after ABZ\_EN is enabled, the device captures the current angle as an absolute position. It then outputs a series of AB pulses to represent this angle.

$$\text{Pulse Count} = \left(\frac{\min(\text{Angle}, 65536 - \text{Angle})}{65536}\right) \times \text{PPT}$$

For example, if the angle is  $90^\circ$  (16384 in count) and PPT =511, then AB outputs 128 pulses. If the angle is greater than  $180^\circ$ , the AB output is reversed, counting down from  $360^\circ$ .

### 8.4 ABZ Startup Delay

The ABZ startup delay can be configured using the  $ABZ\_START\_T[3:0]$  register. Typical settings are:

Table 10: ABZ Startup Delay Settings

| Delay Time       |

|------------------|

| 10 ms            |

| 20 ms (default)  |

| 30 ms            |

| 40 ms            |

| $50~\mathrm{ms}$ |

| 75 ms            |

| 100 ms           |

|                  |

This setting helps prevent false ABZ signals during system power-up instability.

### 9 UVW Output

Figure 18: UVW Output Register Configuration

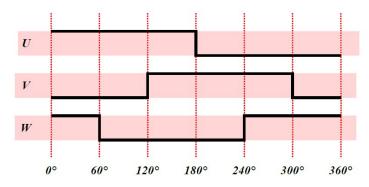

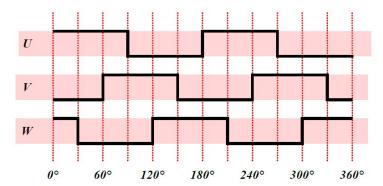

UVW output signals simulate three Hall switches used for commutation in three-phase motors. As shown in Figure 19, the three logic signals have 50% duty cycle and  $120^\circ$  phase difference.

If the motor has more pole pairs than the target magnet, KTH7112 can divide one electrical rotation into multiple commutation steps to generate multiple UVW periods.

The parameter register  $0 \times 7$  uses NPP [4:0] to configure the simulated pole-pair number and UVW switching step angle.

Table 11 describes the NPP configuration:

For example, with a four-pole (two pole-pair) motor, the UVW commutation step is  $30^{\circ}$  per state, as shown in Figure 20.

Figure 19: UVW Output for One Pole Pair

Table 11: UVW Pole-Pair Configuration: NPP[4:0]

| NPP(4:0) | Pole Pairs | States Per Turn |

|----------|------------|-----------------|

| 00000    | 1          | 6               |

| 00001    | 2          | 12              |

| 00010    | 3          | 18              |

| 00011    | 4          | 24              |

| 00100    | 5          | 30              |

| 00101    | 6          | 36              |

| 00110    | 7          | 42              |

| 00111    | 8          | 48              |

| :        | :          | :               |

| 11110    | 31         | 186             |

| 11111    | 32         | 192             |

Figure 20: UVW Output for Two Pole Pairs

### 9.1 UVW Startup Delay

The startup timing of UVW output is the same as ABZ output. It is controlled by the abz\_start\_t[3:0] parameter. This ensures UVW outputs are enabled only after the system becomes stable during power-up.

### 9.2 UVW and Z Signal Phase Relationship

The UVW signals are phase-aligned with the Z signal edge. This alignment ensures proper commutation synchronization with the electrical zero reference position.

### 10 PWM Absolute Output

KTH7112 provides a single-wire PWM absolute angle output mode. PWM is the default output function on pin 9, as shown in Figure 21.

Figure 21: PWM Register Diagram

### 10.1 PWM Frequency Setting

The PWM output frequency is controlled by the 16-bit parameter  $pwm_f$ . The relationship between frequency and  $pwm_f$  is given by:

$$\text{PWM(Hz)} = \frac{(120.284 - 3846.0)}{65536.0} \cdot \text{pwm\_f} + 3846.0$$

Typical settings:

- pwm f = 0: Output frequency is 3846 Hz

- pwm f = 65535: Output frequency is 120.284 Hz

The required frequency accuracy is  $\pm 5\%$ .

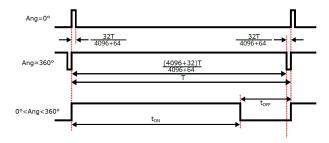

### 10.2 PWM Resolution and Angle Calculation

The PWM signal duty cycle is proportional to the magnetic angle. The output resolution is 12 bits.

- When duty cycle is  $\frac{32}{4096+64}$ , the angle is  $0^{\circ}$

- When duty cycle is  $\frac{4096+32}{4096+64}$ , the angle is  $360^\circ$

The formula to calculate angle from duty cycle is:

$$\mathsf{Ang} = \frac{360}{4096} \left( \frac{(4096 + 64) \cdot t_{\mathsf{ON}}}{t_{\mathsf{ON}} + t_{\mathsf{OFF}}} - 32 \right)$$

where:

–  $t_{\rm ON}$ : PWM high level time –  $t_{\rm OFF}$ : PWM low level time

Figure 22: PWM Output Timing Diagram

# 10.3 PWM Status Indication During Non-Linear Calibration

During automatic nonlinear calibration, the PWM output indicates calibration status:

- 3.8 Hz with 50% duty cycle: calibration in progress

- Constant high level: calibration successful

- Constant low level: calibration failed

After calibration, when the auto\_cal signal is pulled low, PWM returns to normal angle output mode.

### 10.4 PWM Startup Delay

The PWM output is also affected by the abz\_start\_t[3:0] parameter. This ensures that PWM signals start only after system stabilization upon power-up.

### 11 Automatic Nonlinearity Calibration

Figure 23: Registers related to ANLC (Auto Nonlinearity Calibration)

KTH7112 includes an automatic nonlinearity calibration (ANLC) function. It effectively compensates for nonlinearity errors that occur due to installation offsets or imperfect magnetic field distribution, improving angle measurement accuracy.

### 11.1 Calibration Principle

During calibration, the system collects angle error data at 16 evenly spaced points within one full rotation. Using these points, the chip calculates correction parameters and applies real-time output compensation.

During the calibration process, the PWM output flashes at  $3.8~{\rm Hz}$  with a 50% duty cycle to indicate that calibration is in progress. Once calibration is complete, the PWM output returns to normal operation.

#### 11.2 Calibration Status

The register ANLC STATUS[1:0] reflects the current calibration state:

### 11.3 Calibration Methods

KTH7112 supports two ways to trigger ANLC:

Table 12: Calibration Status via ANLC STATUS[1:0]

| Value | Description             |

|-------|-------------------------|

| 0     | Calibration not started |

| 1     | Calibration in progress |

| 2     | Calibration failed      |

| 3     | Calibration completed   |

- 1. **Register-triggered:** Set REG\_CAL to 1 to start nonlinearity calibration.

- 2. **Pin-triggered:** Pull the AUTO\_CAL pin high and hold for a period. The system will automatically determine whether to perform zero position setting or ANLC based on the angle behavior.

#### 11.4 Calibration Guidelines

To ensure optimal calibration results:

- 1. Keep the magnetic field stable and avoid movement between the magnet and sensor.

- 2. Maintain a constant rotation speed during calibration. A recommended speed is 100 to 1000 rpm. Too high or too low speed may affect the result.

- 3. Perform calibration under actual application conditions to capture real-world error.

- 4. For off-axis installations, configure GAINTRIM parameters before ANI C.

- 5. After calibration, parameters are automatically written to MTP and will be retained after power-off.

### 12 System Operation Settings

Figure 24: System Operation Related Registers

### 12.1 Rotation Direction

The rotation direction is configured via the RD bit in register  $0 \times 02$ . It determines whether clockwise or counter-clockwise rotation increases the output angle.

- When RD = 1 (default): Viewed from above the chip, clockwise rotation increases the output angle.

- When RD = 0: Counter-clockwise rotation increases the output angle.

Figure 25: Rotation Direction and Angle Output Relationship

### 12.2 Zero Position Setting

The chip supports both automatic and manual zero alignment.

### 12.2.1 Automatic Zero Setting

**Method 1: Register Triggered** Setting AUTO\_ZERO\_SET = 1 will trigger zero alignment. The chip executes:

1. Calculate:

$$zero\_set\_angle = \begin{cases} ZERO - angle, & if RD = 1\\ ZERO + angle, & if RD = 0 \end{cases}$$

- 2. Write result to ZERO[15:0] register.

- 3. Write to MTP.

- 4. AUTO ZERO SET bit clears automatically.

**Method 2: Pin Triggered** Pulling AUTO\_CAL pin high for more than 2 s will trigger zero setting:

- The chip captures the current angle as zero.

- Writes it to MTP memory.

#### 12.2.2 Manual Zero Position Setting

Manual zero setting is implemented by directly writing to the  ${\tt ZERO[15:0]}$  register.

- Register range: 0 to 65535, representing 0° to 360°

- Written value takes effect immediately and affects all output interfaces

- Value is volatile and will be lost on power-off unless saved via MTP programming

The effect of the ZERO value on angle output is as follows:

• If RD = 0:

$$Angle_{out} = Angle_{raw} - ZERO$$

• If RD = 1:

$${\rm Angle_{out} = Angle_{raw} + ZERO - 65536}$$

Table 13: Comparison of Zero Setting Methods

| Method                       | Advantages                      | Disadvantages                       |

|------------------------------|---------------------------------|-------------------------------------|

| Register-based ZERO setting  |                                 |                                     |

| AUTO_CAL pin based setting   | No communication, easy to use   | Requires additional control pin     |

| Manual ZERO register setting | High accuracy, flexible setting | Must be saved via SPI, more complex |

The ZERO[15:0] register defines the zero position and applies to all output types with 16-bit resolution.

#### **ZERO Value Calculation**

• If RD = 1:

$${\tt ZERO} = 2^{16} - \left(\frac{{\sf Desired\ Angle}}{360^{\circ}} \times 2^{16}\right) + 1$$

• If RD = 0:

$${\tt ZERO} = \left(\frac{{\sf Desired\ Angle}}{360^{\circ}} \times 2^{16}\right)$$

**Example** If RD = 1 and SPI outputs 16384 (i.e.,  $90^{\circ}$ ), set ZERO = 49152, output becomes  $0^{\circ}$  If RD = 0 and SPI outputs 16384, set ZERO = 16384, output becomes  $0^{\circ}$

### 12.3 Hysteresis

Hysteresis refers to the introduction of lag effects on output signals to prevent false switching and improve the system's anti-interference capability. Lag means that the output signal must exceed a specific threshold before it can change its state. This lag effect can effectively reduce noise and other interference effects on the output signal. When the input signal changes, the output signal will not immediately follow the change, but needs to exceed a threshold before changing state. This threshold setting makes the system insensitive to small amplitude noise and interference, thereby improving the stability and accuracy of the system.

The hysteresis function is effective for all output interfaces.

Hysteresis parameters can be configured through the RAM\_HYS [14:0] register,  $1\,\text{LSB} = \frac{360^\circ}{32768} \approx 0.01099^\circ.$  The default value is 7, which is approximately  $0.07693^\circ.$  By introducing output hysteresis, errors can be reduced and the anti-interference capability of the system can be improved. This is very important for applications that require high precision and stability, especially in noisy environments or situations with interference.

Table 14: Hysteresis Parameter Configuration Table

| RAM_HYS[14:0] | Hysteresis Angle (°) | Description        |

|---------------|----------------------|--------------------|

| 0             | 0                    | No hysteresis      |

| 1             | 0.01099              | Minimum hysteresis |

| 2             | 0.02197              |                    |

| 4             | 0.04395              |                    |

| 7             | 0.07693              | Default            |

| 8             | 0.08789              |                    |

| 16            | 0.17578              |                    |

| 32            | 0.35156              |                    |

| 64            | 0.70313              |                    |

| 128           | 1.40625              | Maximum hysteresis |

The hysteresis angle is calculated as:

$$\text{Hysteresis Angle} = \frac{\texttt{RAM\_HYS} \times 360^{\circ}}{32768}$$

### 12.4 Digital Filter

The depth of the digital filter affects both noise immunity and system dynamic response. It is configured by the FW[7:0] register.

- Higher filter level → higher effective resolution

- Lower filter level → faster response

- Default value: 0x88

Table 15: Effective Resolution vs. Filter Depth

| FW[7:0] | Filter Level | Effective Resolution (bit) |

|---------|--------------|----------------------------|

| 0x00    | 0            | 9.5                        |

| 0x11    | 1            | 10                         |

| 0x33    | 3            | 11                         |

| 0x77    | 7            | 12                         |

| 0x88    | 8            | 13                         |

| 0xAA    | 10           | 14                         |

| 0xFF    | 15           | 15                         |

### 13 Product Selection Guide

Table 16: Product Selection Table

| Model   | Noise (1 sigma) | Output Interface   | Time Constant $\tau$ (ms) | Operating Magnetic Field | Application           |

|---------|-----------------|--------------------|---------------------------|--------------------------|-----------------------|

| KTH7112 | 0.015°          | SPI, SSI, PWM, ABZ | 0.51                      | 30−150 mT                | Industrial Automation |

# **14 Ordering Information**

Table 17: Ordering Information

| Model        | Package Type | Operating Temperature | Application           | Number of Pins | CRC Check |

|--------------|--------------|-----------------------|-----------------------|----------------|-----------|

| KTH7112-QN16 | QFN3×3-16L   | -40°C to 125°C        | Industrial Automation | 16             | No        |

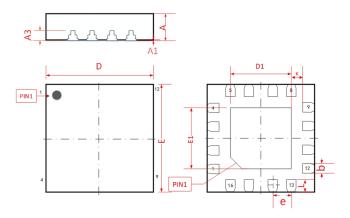

# 15 QFN-16L Package Information

### 15.1 Package Drawing

Figure 26: QFN-16L Mechanical Drawing

### 15.2 Mechanical Dimensions

Table 18: QFN-16L Package Dimensions (Unit: mm)

| Symbol | Min       | Тур    | Max  |  |  |

|--------|-----------|--------|------|--|--|

| Α      | 0.70      | 0.75   | 0.80 |  |  |

| A1     | 0.00      | 0.02   | 0.05 |  |  |

| A3     | 0.203 REF |        |      |  |  |

| D      | 3         | .00 BS | С    |  |  |

| Е      | 3.00 BSC  |        |      |  |  |

| D1     | 1.50      | 1.80   |      |  |  |

| E1     | 1.50      | 1.65   | 1.80 |  |  |

| k      | 0.        | 385 BS | SC . |  |  |

| b      | 0.18      | 0.24   | 0.30 |  |  |

| е      | 0.50 BSC  |        |      |  |  |

| L      | 0.19      | 0.29   | 0.39 |  |  |

## 16 QFN-16L Tape and Reel Information

### 16.1 Package Drawing

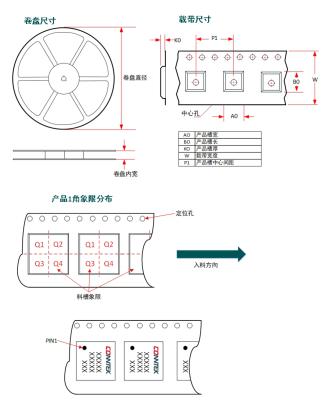

Figure 27: QFN-16L Tape and Reel Mechanical Drawing

### 16.2 Tape Dimensions

Table 19: Carrier Tape and Reel Parameters

| Package Type | Pins | SPQ  | Reel Diameter | Reel Width | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Direction |

|--------------|------|------|---------------|------------|---------|---------|---------|---------|--------|----------------|

| QFN3×3-16L   | 16   | 5000 | 330           | 12.4       | 3.35    | 3.35    | 1.13    | 8.00    | 12.00  | Q1             |

# 17 Reflow Soldering Temperature Profile

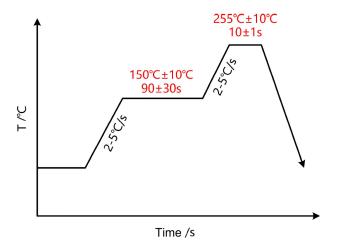

The recommended reflow soldering profile is shown below. It follows a standard ramp-soak-peak process.

### 17.1 Profile Parameters

• Preheat stage:  $150^{\circ}\text{C} \pm 10^{\circ}\text{C}$  for  $90 \pm 30$  seconds

• Ramp-up slope: 2-5°C/s

- Peak temperature:  $255^{\circ}\text{C} \pm 10^{\circ}\text{C}$  for  $10 \pm 1$  seconds

- Cooling rate: 2–5°C/s

### 17.2 Temperature Curve

Figure 28: Reflow Soldering Temperature Curve